# AS6031F1

# Flow Firmware – Description and Application Guide

# AS6031F1 Application Note

Revision: 2 Release Date: 2022-12-0202 Document Status: Production

# **Content Guide**

| Сс | ontent Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

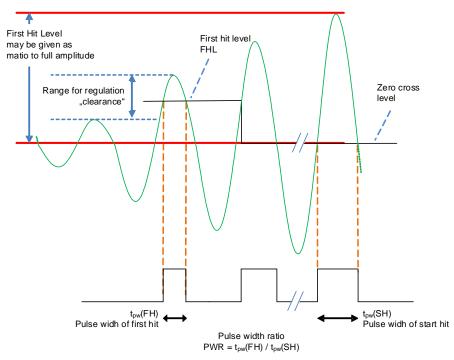

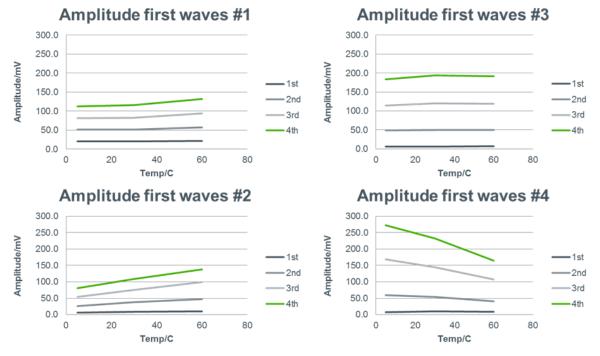

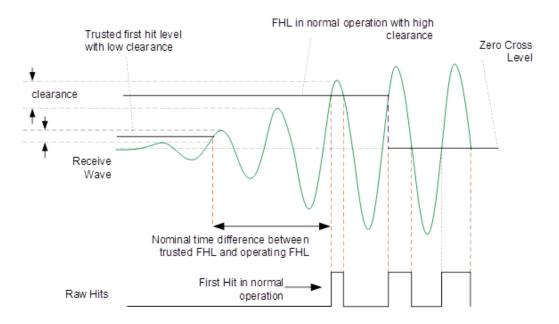

| 1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2  | Firmware Features.52.1Memory Allocation.72.2Major Program Structure82.3Post Processing Subroutines9                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3  | Linearization and Calibration113.1Piece Wise Linear (PWL)12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4  | Phase Shift Detection & Jump Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5  | Firmware Input Data (FWD)175.1Parameters in ScioSense Firmware Data (FWD)175.2Parameters & Flags for General Operation Control225.3Parameters for Hardware245.4Parameters for Medium255.5Parameters for Calibration265.6Parameters for Zero Flow and Negative Flow Operation285.7Parameters for Error Handling295.8Parameters for Error Counters & Interrupts315.9Parameters for FHL Regulation335.10Parameters for Phase Shift Detection355.12Parameters for Temperature Measurement365.13Parameters for Pulse Interface375.14Optional Parameters39 |

| 6  | Firmware Output Data (RAM)406.1Variables and Results in RAM406.1.1Firmware Status Register (RAM_R_FW_STATUS)466.1.2Phase Shift Status Flag Register (RAM_V33_PH_S_STATUS_FLAGS)496.1.3Firmware Error Flag Register (RAM_R_FW_ERR_FLAGS1)506.2Firmware Variables in RAM-part of FWD536.3Reading Data546.3.1Reading via GUI56                                                                                                                                                                                                                          |

| 7  | First Hit Level Setting       57         7.1 First hit level selection criteria       57         7.2 First Hit Level Regulation Methods       61         7.2.1 Method 1: Keep FHL constant       62         7.2.2 Method 2: Return to Trusted FHL       63         7.2.3 Method 3: Offset Trusted FHL       63                                                                                                                                                                                                                                       |

| 8  | Error Handling and Operation Safety658.1Error Handling8.2Error Handling Flow Chart68                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8  | 3.3<br>3.4<br>3.5 | Error Counters<br>Error Interrupt<br>Error Signals through Pulse Interface | 70 |

|----|-------------------|----------------------------------------------------------------------------|----|

| 9  |                   | le to Operation - Step by Step                                             |    |

|    | 9.1               | A First Impression                                                         |    |

|    | ).2               | Setup and Customization                                                    |    |

|    | 9.3               | Creating and downloading a firmware data file                              |    |

|    | 9.3.              |                                                                            |    |

|    | 9.3.              |                                                                            |    |

|    | 9.3.              |                                                                            |    |

| Ģ  | 9.4               | Calibration process in development and production                          |    |

| 10 | Add               | ing Custom Code to ScioSense FW                                            | 81 |

|    | 10.1              | Editing and Compiling                                                      |    |

|    | 10.2              | Sample Code                                                                |    |

| 11 | مم                | endix                                                                      | 87 |

|    | дрр<br>11.1       | Firmware Input Data Overview (FWD)                                         |    |

|    | 1.7               | Firmware Version Numbers                                                   |    |

|    | 1.3               | Firmware Related Files                                                     |    |

|    | 11.4              | Notational Conventions                                                     |    |

|    | 1.5               | Abbreviations                                                              |    |

|    | 11.6              | Glossary                                                                   |    |

| 12 | Сор               | yrights & Disclaimer                                                       | 02 |

| 13 | Revi              | sion information                                                           | 02 |

AS6031F1 is a variant of the AS6031 ultrasonic flow converter that comes with a protected flow firmware by ScioSense already programmed into the NVRAM. Based on these algorithms and together with the appropriate calibration and operation parameters the chip is ready to do the complete flow and volume calculation as well as error handling on chip. This brings great advantage with respect to power consumption of the whole system.

In this application note we describe the operation of the firmware in principle, the base parameters as stored in the firmware data and the output data provided in the RAM.

## 1 Introduction

This application note describes the ScioSense firmware version as implemented in the ultrasonic flow converter AS6031F1. It describes the functionality of the firmware, the organization and format of the input data as well as of the output data.

Why should we have the flow calculation in the AS6031? Flow calculation in ultrasonic flow meters is a complex task, using many inputs from the analog frontend like time-of-flight, pulse width and amplitude. The conversion from time-of-flight (ToF) to flow demands linearization and calibration. For short- and long-term operation stability, a complex error handling is needed, which is based on hardware error flags but also data analysis. And all this should be achieved with lowest power consumption.

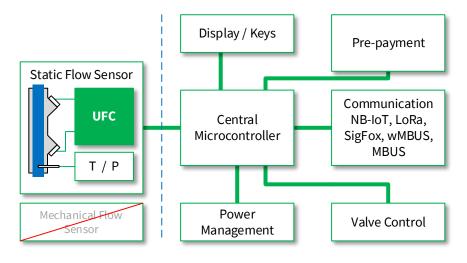

#### Figure 1: Ultrasonic Flow Meter Block diagram

ScioSense designed a dedicated firmware that covers all this and provides several advantages to the user:

- Fast time to market. The user can focus on other tasks like spool piece design, characterization and calibration. No need to program the AS6031.

- Lowest power due to optimized CPU and reduced communication with the external  $\mu P$ . AS6031F1 runs autonomously, so the external  $\mu P$  can sleep most of the time.

- High flexibility in the choice of the external  $\mu$ P. Ideally. Users can continue with their existing platforms, e.g., those being used for mechanical meters, or they select the most appropriate controller available from the shelf.

- The specification for the central µP with respect to connectivity, display and data management will be very volatile, while the flow calculation will be a constant. A split is therefore recommended.

- Flow and volume are available as digital data via SPI. Alternatively, the flow can be output via pulse interface, which can be compatible to mechanical meters.

The ScioSense firmware always aims at operation in flow meter mode, where the chip measures autonomously and indicates the availability of results by an interrupt to the external microcontroller. The configuration is stored as part of the firmware data and copied into the configuration registers after power-on reset. When it is disturbed or interrupted, it will resume nominal operation by a watchdog reset, and when its configuration is modified, it will restore it latest after one hour. Some configurations can't be changed at all but will be controlled by the firmware, see section 5.13 for details.

The right way to stop the firmware and change configurations, for example for testing, is to switch off post processing and disable the watchdog (else a reset happens within typically 13 s). Then any configuration can be tested without firmware operation. For tests with active firmware the desired configuration should be stored in firmware data, see section 9.3.1. With a few exceptions, a modified configuration can be written to the chip directly while the firmware operates. But note that the firmware will restore its stored configuration at any full hour of the built-in real time clock SRR\_TS\_HOUR and SRR\_TS\_MIN\_SEC (0x0E6 and 0x0E7).

## 2 Firmware Features

AS6031F1 comes with ScioSense firmware that does the full flow and temperature calculation. There is no need for the user to write code by himself. Only firmware data need to be adopted with respect to operation limits and linearization coefficients according to the specific sensor. An external controller can read the measurement results like flow and temperature from specified memory cells over SPI on demand. The measurement is running permanently without any need of external control. As an option, users of course can add their own code like additional filtering, averaging or adoption to production process.

Typical properties of the firmware are:

- Flow measurement

- Full linearization and calibration, either using a standard piece-wise linear correction or ScioSense proprietary method.

- Temperature measurement for cold water meters derived from speed of sound (up to 60 °C).

- Temperature measurement using resistive sensors 0.5 to 5 k $\Omega$  with built-in PT1000 characteristic, procedures for 2- and 4-wire measurement and a calculation accuracy in 4-wire mode of 10 mK.

- Optional internal chip temperature measurement.

- Zero flow detection e.g., down to 0.5 l/h for Q3 = 4000 l/h.

- Full communication (input and output) over SPI. Flow volume and error can be provided also over standard two-wire pulse interface.

- Prepared for two-point calibration (zero flow and high flow @ room temperature) in series production.

- First-hit level (FHL) regulation, various modes.

- Phase shift detection and phase jump correction for ToF

- Bubble detection and error detection included to recognize wrong measurements.

- Entry points for custom code.

Hardware related:

- Firmware NVRAM usage (of 4 kB available): 2.9 kB. 546 B for phase shift.

- RAM usage (of 176 x 32-bit words):

- 109 words permanently used, including 27 words frontend data buffer (FDB).

- 21 words free / unused 19 words free for temporary use.

- Firmware data usage (of 128 x 32 words):

- 11 words configuration (always) plus protected ones.

- 96 words used, including 16 words for bootloading.

- 7 words free, up to 27 depending on linearization & calibration.

- Expected total current consumption including the flow calculation and 2 V/V gain at 3.0 V (example):

- About 13  $\mu$ A @ 8 Hz flow measuring rate, about 5  $\mu$ A @ 2 Hz flow measuring rate.

For any information related to the hardware of the AS6031 like configuration registers, system handling registers, error flags and general operating principle please refer to:

AS6031 datasheet SC-000853-DS.

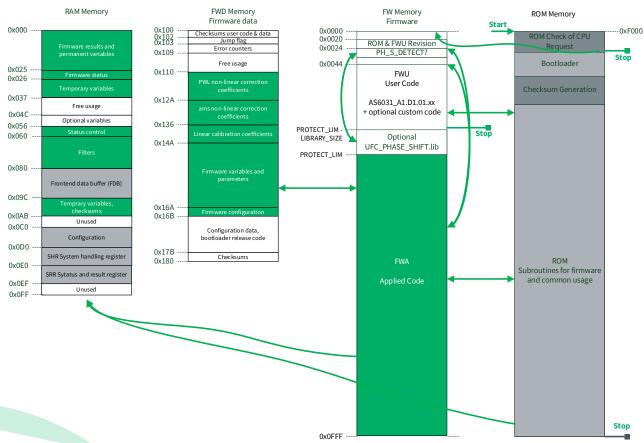

#### 2.1 Memory Allocation

The ScioSense firmware uses memory in the following way:

- The firmware user code (FWU) is the main program, located in the lower part of the NVRAM. It is open sources and can be customized. It is limited in size by the ScioSense code. Register PROTECT\_LIM shows the limit, e.g., 1216 (address 0x4C0) bytes in case of ScioSense applied firmware revision A1A10314.

- The applied ScioSense code (FWA) calls subroutines in the user code (FWU). FWA takes roughly 3 k of NVRAM. This part is closed and write/read protected.

- Many support functions are coded in ROM. This increases the efficiency of the programming. In addition, the ROM starts with a check for the CPU request and a bootloader section.

- The firmware data hold the individual data, namely the non-linear correction coefficients, the 2-point calibration coefficients, other firmware variables and parameters as well as the configuration of the chip.

- In the RAM, the original front end buffer data are stored as well as the final data calculated by the flow firmware. Of course, several cells are used for filter functions and temporary variables.

Figure 2: Memory allocation

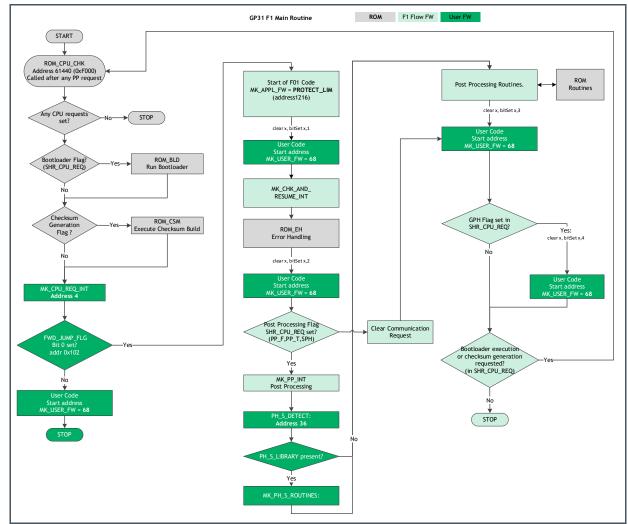

#### 2.2 Major Program Structure

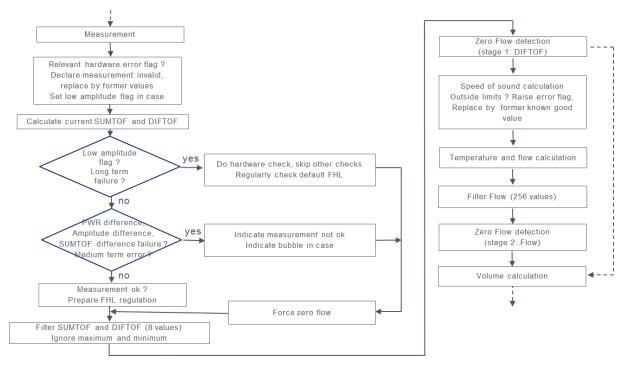

The CPU gets called with every measurement. The main procedures are:

- First, the reason for the call is checked. ROM routine ROM\_CPU\_CHK is called, which checks the CPU request flags.

- Next, bootloader flag and checksum generations flags are checked by ROM routines.

- From there, the open user code starts at address 4, with checking firmware data cell 2 for bit 0. If this is zero, then only the user code is executed, and the CPU stops at the end. If this bit is 1 then the applied ScioSense code is started.

- The applied code has four indirect jumps into the open user code.

- At the very beginning

- After error handling

- After postprocessing

- For general purpose handling

- Following the first jump at the beginning, the applied firmware does some basic initialization and restoration as well as basic operation check routines. Subtasks of these check-and-resume routine are:

- Refresh permanent RAM data by an hourly recall. Solves issues by corrupted data.

- Check initialization and restore if needed.

- Keep data and flags of running operation.

- Check whether ROM is powered.

- Check initialization and re-initialize if needed.

- Break infinite loops.

- Restore constants after a recall.

- Restore the operation state after a recall.

- Before postprocessing the applied code jumps into the open part for the phase jump detection and correction at address 36. This part is executed only when the library is included.

The main post processing routines do the following:

- Low-level error handling (hardware level).

- Handle and clear all hardware error flags / refresh copy in firmware error register.

- Set / reset error counters.

- Erase / replace invalid results.

- Invalid flow results are replaced by valid predecessors (up to 8).

- Invalid TM results are cleared immediately, with calculation results replaced by 0x7FFFFFF (last valid results kept elsewhere).

- Post-processing subroutines

The whole process is controlled by interrupt requests issued by the chip's measurement rate generator (MRG) and the task sequencer (TS).

Figure 3: Flow chart, top level

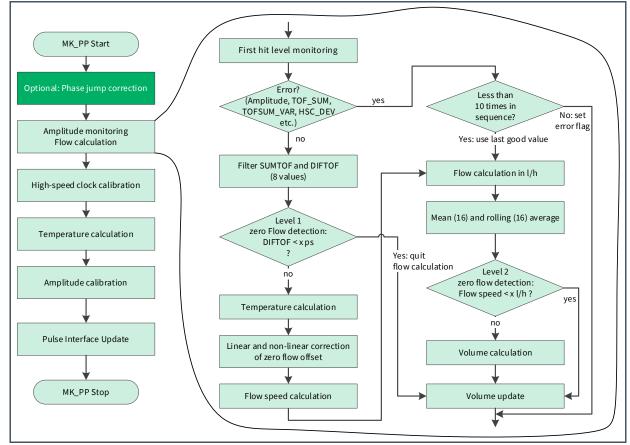

#### 2.3 Post Processing Subroutines

The most important routines are the post processing routines, therefore some more details on those:

- Temperature calculation

- The sum TOF\_UP + TOF\_DOWN is used to calculate the speed of sound. The physical relation between speed of sound and temperature is then used to calculate the temperature, limited to the range < 60 °C.</li>

- Calculating temperatures based on the RDC measurements with the internal sensors and the external cold and hot sensors. This includes the compensation measurements in 2-wire and 4-wire mode.

- Flow calculation.

- First hit level monitoring and regulation, based on pulse width ratio or amplitude variation.

- Filtering (rolling (8) average of DIF\_TOF and SUM\_TOF).

- Zero flow detection (stage 1: zero flow will skip flow calculation for power saving reasons).

- Flow speed calculation (linear and non-linear correction).

- Mean (16) and rolling (16) average.

- Zero flow detection (stage 2).

- Volume calculation.

- High-speed clock calibration.

- Amplitude measurement and calibration.

- Pulse interface data generation.

Figure 4: Main post processing routine

The phase jump detection and correction of the TOF UP and TOF DOWN are implemented in an open user code snippet and a related library file. See section 4 for details.

# 3 Linearization and Calibration

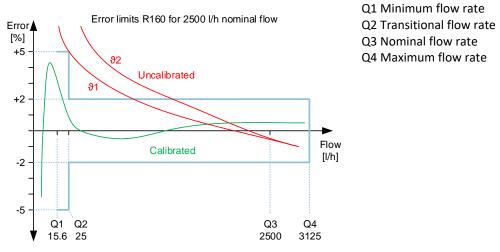

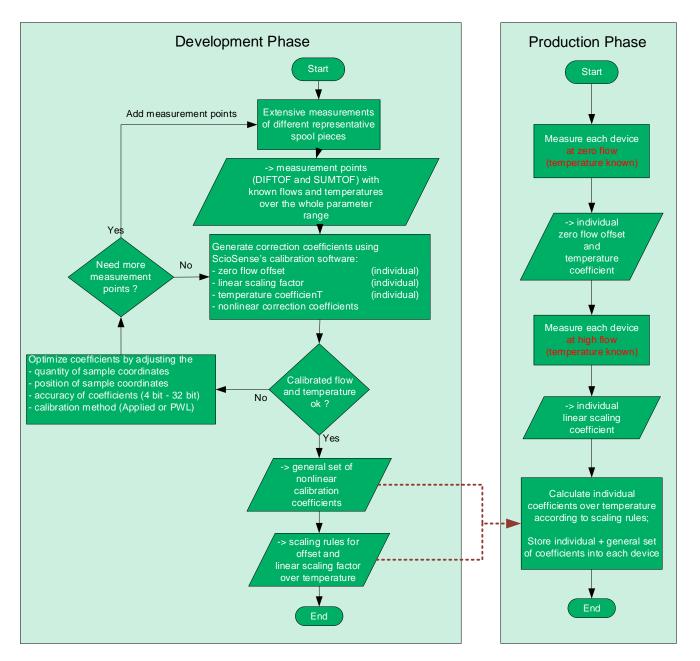

The firmware converts the difference in time-of-flight up and down (DIFTOF) into a flow and volume information. Ideally, the relation between DIFTOF and flow speed would be linear, but in addition to a temperature dependance of the linear relation, there is also a non-linear deviation that is related to the hydraulics of the specific sensor design. The F01 firmware concept assumes that the non-linear behavior is more or less the same over one or more production lots and that the individual meters can be corrected linearly at two points.

Figure 5: Non-linear correction

Linearization is done in three major steps:

- 1 Offset correction. This is necessary to get a correct sum of time-of-flight up and down (SUMTOF) which then is used to calculate the speed of sound and the temperature, which is then used for the temperature correction.

- 2 Linear correction over 2 points. This is the rough, linear correction for the individual meter, with offset and slope values for tree temperature ranges.

- 3 Non-linear correction. The firmware offers two options for this: a classical piecewise linear correction (PWL) or a ScioSense specific one that corrects for deviations to one direction at low flow very effectively.

The non-linear coefficients are generated during development phase and typically fix for a product or at least a production batch. In production, the coefficients for the 2-point linear correction and the offset are updated individually. But even individual PWL coefficients could be adjusted with some additional computing.

All calibration parameters are generated by the calibration engine (new engine in preparation). Cells number 58 and 62 to 73 have to be adapted to individual spool pieces by 2-point calibration. Note that the address range for PWL coefficients can be selected through B0 of *FWD\_FW\_CONFIG* to optimize memory space needs. Usually only one calibration method is used, and the coefficients of the other one are not stored. But to some extend it is possible (if there is still enough space for all PWL coefficients) to have both types of calibrations stored, such that a simple comparison can be done just by switching between ScioSense and PWL method.

In step1 the parameters for a correct offset and in the following the speed of sound and temperature calculation are set. The distances with flow and with no flow describe the mechanical design. The SUMTOF offset is collected as a first measurement in 2-point calibration. The DIFTOF at high flow is used by the ScioSense algorithm only.

In step 2 the DIFTOF is corrected in a linear manner, means by an offset O(T) and a scaling factor F(T). For the offset, the calibration engine output is base offsets O(TCx) and slopes (S\_O(TCx) for three temperatures and allows a precise offset interpolation:

$O(T) = O(TCx) + S_O(TCx)^*(TCx - TC_{measured}) / f_{ref}$

A simplified approach would use only one offset and slope factor for the complete temperature range.

The measured DIFTOF is corrected by this offset O(T).

In step 3, this DIFTOF is further corrected by the non-linear parameter, e.g. with PWL by subtracting the PWL output.

In step 4, the scaling factor from the linear 2-point correction is applied. The procedure for the scaling factor is similar, base factors F(TCx) and slopes (S\_F(TCx) for three temperatures allow a precise scale factor interpolation:

$F(T) = F(TCx) + S_F(TCx)^*(TCx - TC_{measured}) / f_{ref}$

The DIFTOF is corrected by this offset slope F(T), multiplied with the speed of sound and divided by the active length to get the flow velocity.

3.1 Piece Wise Linear (PWL)

The PWL coefficients are generated by means of the calibration engine that can be downloaded from https://downloads.sciosense.com/AS6031/. This engine offers some flexibility with respect to the number of calibration points, but total number and size is limited by the available space foreseen in the firmware data. By default, the address range 16 to 41 is foreseen. The starting address is set in cell 106, bits 7:0, PWL\_ADR. Without restrictions it can be set to 7. It can be set also to 3, but then the error counters cannot be activated. The range stops normally at address 41. But also the range for the ScioSense coefficients can be used which ends at address 53. In total we have 25 to 50 32-bit words available.

The format of the coefficients can be set to 4, 8, 16 and 32 bits. With 32 bit values the number is quite limited, so 16 bit or even 8 is the choice for high numbers of coefficients, of course with loss in precision. This format is defined in the calibration engine.

In general, the organization of the PWL coefficients in the firmware data is defined in the first word of PWL firmware data, *FWD\_COEFF\_ORG*:

- Bits [31:30]: DIF\_TOF coefficient size, 4, 8, 16 or 32 bits.

- Bits [29:28]: 8-bit temperature values, position after decimal point, 0, 1, 2 or 3.

- Bits [23:16]: Number of temperature points

- Bits [7:0]: Number of DIF\_TOF points

**Note:** The PWL linearization algorithm does not cover handling of negative coefficients. When the calibration engine output includes negative coefficients, all coefficients have to be increased by the absolute value of the smallest negative coefficient so that all are positive. Those corrected coefficients can then be written into the firmware data. The value of the smallest negative value is put into FWD cell 88, *FWD\_CORR\_COEFF*.

| DIFTOF | T1 | I          | T2       | Т3         | T4         |   | Minimum:    |      | DIFTOF | T1       | T2       | Т3       | T4       |

|--------|----|------------|----------|------------|------------|---|-------------|------|--------|----------|----------|----------|----------|

| 0      | )  | 19         | 29       | 40         | 50         |   | -1,0568938  |      | 0      | 19       | 29       | 40       | 50       |

| 22     |    | 1,7922297  | 1,113182 | 0,73147691 | 1,6010345  |   |             |      | 22     | 2,849123 | 2,170075 | 1,788371 | 2,657928 |

| 46     | 1  | ,82892941  | 1,486948 | 1,30713696 | -0,2465813 | > | Add 1,05689 | 938> | 46     | 2,885823 | 2,543842 | 2,364031 | 0,810312 |

| 99     |    | 2,1624493  | 1,510421 | 1,55300598 | -1,0568938 |   |             |      | 99     | 3,219343 | 2,567315 | 2,6099   | 0        |

| 211    | 2  | 2,20838017 | 1,438918 | 0,6066375  | 1,1991559  |   |             |      | 211    | 3,265274 | 2,495812 | 1,663531 | 2,25605  |

| 450    | )  | 0          | 0        | 0          | 0          |   |             |      | 450    | 1,056894 | 1,056894 | 1,056894 | 1,056894 |

Figure 6: Example negative coefficients

*FWD\_CORR\_COEFF* = T<sub>ref</sub> 2<sup>16</sup>/-1.0568938 = -277.058 = 0xFFFFEEA

T<sub>ref</sub> = Time period of high-speed clock

# 4 Phase Shift Detection & Jump Correction

#### 4.1 Functionality

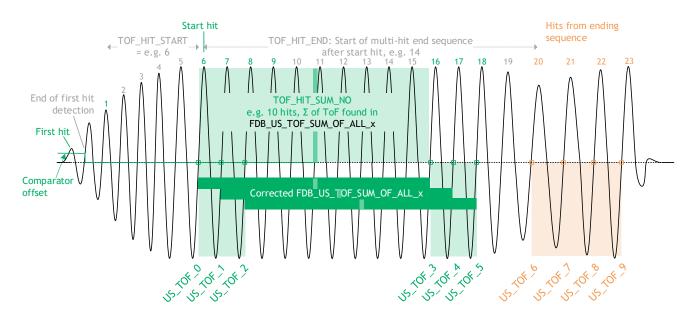

AS6031 has the possibility to fire a split burst with a phase shift of typically  $^{3}/_{4}$  T between initial and ending sequence.

#### Figure 7: Split fire burst

The idea is to have the jump after the hits that are used for ToF measurement. The content of the frontend data buffer is adjusted and shows only the ultrasonic TOF sum of all values Up and Down, **FDB\_US\_TOF\_SUM\_OF\_ALL\_x**. The individual ToF in the RAM show the values for the very first three hits measured, the three hits following the original measurement and four hits that are exposed to the phase shift.

#### Figure 8: Phase shift detection and jump correction

The hits of the ending sequence are used to find the position of the phase jump. Therefore, they are compared with the theoretically expected time stamps without phase jump. US\_TOF\_3 is taken as basis and multiples of the period are added for the expected times. The differences are temporarily stored in RAM cells RAM\_Vxx\_PH\_S\_xx\_x. The biggest delta is the taken as a reference and used to decide whether the position of this jumped into one or the other direction.

The ToF result can be corrected mathematically. In the normal case, the result from the front-end data buffer is corrected by US\_TOF\_1 and US\_TOF\_4 to the center position. In case of a phase jump it shifted towards US\_TOF\_0/ US\_TOF\_3 or US\_TOF\_2/ US\_TOF\_5.

| Nor | mal:                | Jump right: |           | Jump lef | t: |         |    |         |    |

|-----|---------------------|-------------|-----------|----------|----|---------|----|---------|----|

| 37  | RAM_V2F_PH_S_DOWN_0 | 000006B2    | 0.0038147 | 6.538    | ns | 0.294   | ns | 42.362  | ns |

| 38  | RAM_V30_PH_S_DOWN_1 | 00002AF8    | 0.0038147 | 41.962   | ns | 6.966   | ns | 177.998 | ns |

| 39  | RAM_V31_PH_S_DOWN_2 | 0000B48E    | 0.0038147 | 176.323  | ns | 42.023  | ns | 317.951 | ns |

| ЗА  | RAM_V32_PH_S_DOWN_3 | 00014502    | 0.0038147 | 317.391  | ns | 176.693 | ns | 340.317 | ns |

Figure 9: Example of temporary phase deviations

The major parameter in the firmware data to be defined by the application is the parameter *FWD\_PH\_S\_THRESHOLD*. This is the absolute value of phase-shift threshold value (no negative values here). The format is fd16 in multiples of the reference period (value/ $2^{16} * T_{ref}[ns]$ ).

In the example above this threshold could be e.g. 80ns. If the value of *RAM\_V31\_PH\_S\_DOWN\_2* falls below that value then there was a jump to the right. If *RAM\_V30\_PH\_S\_DOWN\_1* is bigger than that threshold there was a shift to the left.

The measured TOF results in FDB 0x080 and 0x084 will be corrected in the following manner:

- No jump: SUM\_OF\_ALL\_U = SUM\_OF\_ALL\_U TOF\_0\_U + TOF\_3\_U

- Jump right: SUM\_OF\_ALL\_D = SUM\_OF\_ALL\_D

- Jump left: SUM\_OF\_ALL\_D = SUM\_OF\_ALL\_D TOF\_0\_U + TOF\_3\_U TOF\_1\_D + TOF\_4\_D

- 4.2 Implementation

The phase shift detection and jump correction routine is not hard-coded but needs to be implemented in the open user code. The necessary line in the code will be #include "UFC\_PHASE\_SHIFT.lib".

Sample code is provided by ScioSense as a library file. The ScioSense flow firmware jumps to address 36 to execute the phase shift routine in advance to the further flow calculation.

The flow firmware always jumps to label PH\_S\_DETECT. If the phase-shift library has been included the code inside the #ifdef PH\_S\_LIBRARY will get compiled and executed at each jump. If the phase-shift library hasn't been included, then the code line jsubret will get compiled and the code will return from jump immediately.

```

32

ora

equal1 FW_ROMVERSION_REV

equal FW VERSION

; Defined at the beginning of this file

org 36

PH_S_DETECT:

#ifdef PH S LIBRARY

jsub MK PH S ROUTINES

; jump to call every phase-shift routine

jsubret

#else

jsubret

#endif

org 64

MK_USER FW:

```

The library routine has sub routines for

- Initialization (TOF\_HIT\_NO, period)

- Consistency check for the individual ToF results

- Calculation of the deviations

- Check for the presence of a phase jump

- Correction of the TOF\_SUM, overwriting the original results in the frontend data buffer, addresses 0x080 and 0x084.

Note: In case the library is not included the code jumps back immediately for normal flow calculation. But the address range 36 to 68 is reserved so that it is possible to have custom code, other than the jump to the phase shift routine.

# 5 Firmware Input Data (FWD)

Most of the values in various cells of the firmware data should be customized or at least checked. Section 4.1 gives a complete overview of all firmware data parameters. The quickest start with ScioSense firmware may be checking the parameter table there and use it to customize the template firmware data file provided by ScioSense. If necessary, more detail information can be found in the following sections, which discuss the overview in different segments, ordered for their particular function with focus on the relevant bits.

The major register for operation control is *FWD\_FW\_CONFIG* (cell number 106). Its control bits are summarized in section 5.2.

#### 5.1 Parameters in ScioSense Firmware Data (FWD)

The following list is a complete overview of FWD memory cell usage by the ScioSense firmware. For the format definition, see the appendix on notational conventions.

All variable names and address definitions can also be found in file AS6031\_Flow\_FW\_A1A1.h, contained in the evaluation package. For the physical addresses, add the cell number to base address 0x100.

#### Table 1: Firmware data (FWD)

| Cell <sup>1</sup> | Variable Name         | Function                  | Description<br>default value (if applicable)                                                                                                                    |           |  |  |  |

|-------------------|-----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| 0                 | FWD_FWU_CS            |                           | Checksums                                                                                                                                                       | User code |  |  |  |

| 1                 | FWD_FWDU_CS           |                           |                                                                                                                                                                 | User data |  |  |  |

| 2                 | FWD_JUMP_FLAG         |                           | Flag to trigger jump from ScioSense code to address 68 of the<br>user code.<br>Bit 0 = 0: Direct jump to address 68<br>Any Bit = 1: Indirect jump to address 68 |           |  |  |  |

| 3                 | FWD_ERROR_COUNT_CONF1 |                           | Define error flag positions to be counted in error counter 1                                                                                                    |           |  |  |  |

| 4                 | FWD_ERROR_COUNT_CONF2 | iters                     | Define error flag positions to be counted in error counter 2                                                                                                    |           |  |  |  |

| 5                 | FWD_ERROR_COUNT_21    | Error cour                | Temporary storage of error counts 2 (B3, B2) and 1 (B1, B0)<br>Set to 0x00000000 if error counters are used                                                     |           |  |  |  |

| 6                 | FWD_ERROR_COUNT_43    | (optional) Error counters | Temporary storage of error counts 4 - each error (B3, B2) and 3<br>- hardware errors (B1, B0)<br>Set to 0x00000000 if error counters are used                   |           |  |  |  |

| 7                 | FWD_ERROR_COUNT_INV21 |                           | Inverse of 0x105 for constant checksum                                                                                                                          |           |  |  |  |

<sup>1</sup> Address = Cell number + offset 0x100

AS6031F1 Flow Firmware SC-001493-AN-2 / 2022-12-02 / Preliminary

| 8              | FWD_ERROR_COUNT_INV43       |                             | Inverse of 0x106 for constant ch                                                                                                                               | ecksum                 |                 |  |  |  |

|----------------|-----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|--|--|--|

| 9 to<br>15     | NOT USED                    |                             | Not used                                                                                                                                                       |                        |                 |  |  |  |

| 16<br>to<br>41 | PWL COEFFICIENT TABLE       | ction                       | (optional) Typical position of PW generated by cal. engine                                                                                                     | L calibration coeffici | ents table,     |  |  |  |

| 42<br>to<br>53 | SCIOSENSE COEFFICIENT TABLE | Non-linear correction       | (optional) Fixed position for ScioSense calibration coefficients table, generated by cal. engine                                                               |                        |                 |  |  |  |

| 54<br>to<br>73 | LINEAR COEFFICIENTS TABLE   | Non                         | Linear coefficients table, all generated by cal. engine; values in cells # 58 and 62 – 73 have to be adapted to individual spool pieces by 2-point calibration |                        |                 |  |  |  |

| 54             | FWD_R_TEMP_TC1              |                             | Temperatures for linear calibration                                                                                                                            | on in °C               | 1 <sup>st</sup> |  |  |  |

| 55             | FWD_R_TEMP_TC2              |                             | i omatio io                                                                                                                                                    |                        | 2 <sup>nd</sup> |  |  |  |

| 56             | FWD_R_TEMP_TC3              |                             |                                                                                                                                                                | 3 <sup>rd</sup>        |                 |  |  |  |

| 57             | FWD_R_TEMP_TC4              |                             | 4 <sup>th</sup>                                                                                                                                                |                        |                 |  |  |  |

| 58             | FWD_R_TOF_OFFSET            |                             | Offset time for SUMTOF (fd16*T <sub>ref</sub> )                                                                                                                |                        |                 |  |  |  |

| 59             | FWD_TOF_DIFF_CAL            |                             | DIFTOF at high flow calibration point (fd16*T <sub>ref</sub> )                                                                                                 |                        |                 |  |  |  |

| 60             | FWD_DIST_WITH_FLOW          | oint)                       | Ultrasonic sound path length along flow in m (fd24)                                                                                                            |                        |                 |  |  |  |

| 61             | FWD_DIST_NO_FLOW            | Linear correction (2-point) | Ultrasonic sound path length w/o flow in m (fd24)                                                                                                              |                        |                 |  |  |  |

| 62             | FWD_R_ZERO_OFFSET_TC2       | rrection                    | Zero flow DIFTOF<br>O(TC)                                                                                                                                      | at TC2                 |                 |  |  |  |

| 63             | FWD_R_ZERO_OFFSET_TC3       | iear co                     | Format fd32                                                                                                                                                    | at TC3                 |                 |  |  |  |

| 64             | FWD_R_ZERO_OFFSET_TC4       | Ľ                           |                                                                                                                                                                | at TC4                 |                 |  |  |  |

| 65             | FWD_R_O_SLOPE_TC12          |                             | Zero flow slope<br>S_O(TC)                                                                                                                                     | between TC1 and        | TC2             |  |  |  |

| 66             | FWD_R_O_SLOPE_TC23          |                             | Format fd16                                                                                                                                                    | between TC2 and        | TC3             |  |  |  |

| 67             | FWD_R_O_SLOPE_TC34          |                             |                                                                                                                                                                | between TC3 and        | TC4             |  |  |  |

| 68             | FWD_R_F_SLOPE_TC12          |                             | Proportionality factor slope<br>S_F(TC)                                                                                                                        | between TC1 and        | TC2             |  |  |  |

| 69             | FWD_R_F_SLOPE_TC23          |                             | Format fd16                                                                                                                                                    | between TC2 and        | TC3             |  |  |  |

| 70             | FWD_R_F_SLOPE_TC34          |                             |                                                                                                                                                                | between TC3 and TC4    |                 |  |  |  |

| 71 | FWD_R_F_OFFSET_TC2  |                | Proportionality factor                                                                                                                                               | at TC2                           |  |  |  |

|----|---------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| 72 | FWD_R_F_OFFSET_TC3  |                | F(TC)<br>Format fd16                                                                                                                                                 | at TC3                           |  |  |  |

| 73 | FWD_R_F_OFFSET_TC4  |                |                                                                                                                                                                      | at TC4                           |  |  |  |

| 74 | FWD_SOUND_VEL_MAX   |                | Maximum of speed of sound in m/s<br>Default value for water 0x00061400<br>Format fd8                                                                                 |                                  |  |  |  |

| 75 | FWD_1_BY_A          | elated         | Medium constant, used for T calo<br>sound. Default value for water 0>                                                                                                |                                  |  |  |  |

| 76 | FWD_CONST_C         | Medium related | Medium constant, used for T calculation on basis of the speed of sound. Default value for water 0x000F6C3A                                                           |                                  |  |  |  |

| 77 | FWD_THETA_MAX       | 2              | B3/B2/B1: Temperature at maximum speed of sound in °C,<br>format fd8.<br>B0: minimal speed of sound, format fd5.<br>Default value for water 0x004A002B               |                                  |  |  |  |

| 78 | FWD_LONG_TERM_ERROR |                | Number of low AM measurement<br>water checks are done<br>Proposed value 0x00000020                                                                                   | ts before hardware failure / no- |  |  |  |

| 79 | FWD_FHL_USER        |                | B1/B0: trusted FHL ratio (option<br>or<br>B0: absolute trusted FHL, LSB=0                                                                                            |                                  |  |  |  |

| 80 | FWD_TOF_SUM_DELTA   |                | FHL method 3: Nominal time difference (raw TDC units) in SUMTOF between operating and trusted FHL                                                                    |                                  |  |  |  |

| 81 | FWD_TOFSUM_VAR_LIM  |                | Error limit for deviation of SUMT(<br>TDC units)                                                                                                                     | OF from former average (raw      |  |  |  |

| 82 | FWD_HSC_DEV         |                | Firmware data memory with max the HS clock from 4 LS clock per                                                                                                       |                                  |  |  |  |

| 83 | FWD_ERR_INTERRUPT   |                | Define error flag positions that is<br>RAM_R_FW_ERR_FLAGS1                                                                                                           | sue an interrupt Same bits as    |  |  |  |

| 84 | FWD_AM_DIFF_LIM     |                | Error limit for deviation between<br>UP and DOWN in mV, format fd1                                                                                                   |                                  |  |  |  |

| 85 | FWD_R_AM_MIN        |                | Minimum allowed amplitude in mV, format fd16, must be set to a realistic value, lower than in normal operation, but higher than in no water/hardware error condition |                                  |  |  |  |

| 86 | FWD_PW_NOM          |                | Nominal pulse width ratio with fd<br>off pulse width regulation (0x54 b                                                                                              |                                  |  |  |  |

| 87  | FWD_PW_DEV            |                        | Error limit for deviation between currently measured UP and DOWN pulse width, format fd7                                                                                                        |

|-----|-----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88  | FWD_CORR_OFFSET       |                        | Offset correction in case of negative PWL coefficients; negative value in raw TDC format fd16                                                                                                   |

| 89  | FWD_TOF_RATE_FACTOR   |                        | Factor for TOF rate scaling in zero flow case                                                                                                                                                   |

| 90  | FWD_FLOW_AVG_FACTOR   |                        | 2 <sup>N</sup> number of flow values for averaging; this factor *16 determines the total number of samples for long term averaged flow, as used for the zero-flow decision.                     |

| 91  | FWD_R_PULSE_PER_LITER |                        | Pulse interface: Number of pulses per liter                                                                                                                                                     |

| 92  | FWD_R_PULSE_MAX_FLOW  |                        | Pulse interface & maxflow error limit: maximum permissible flow in l/h.                                                                                                                         |

| 93  | FWD_NEG_FLOW_LIMIT    |                        | Cut-off limit for negative flow in I/h, format fd16; positive values are ignored                                                                                                                |

| 94  | FWD_R_TOF_DIFF_LIMIT  |                        | Minimum limit for DIFTOF values in raw TDC units. At lower<br>[DIFTOF], temporary zero flow is assumed and no calculation is done                                                               |

| 95  | FWD_ZERO_FLOW_LIMIT   |                        | Zero flow limit in I/h, format fd16: When the absolute of the long-<br>term average flow is smaller, long term zero flow is assumed<br>and the TOF rate is scaled by <i>FWD_TOF_RATE_FACTOR</i> |

| 96  | FWD_CAL_PTR_OFFSETR   |                        | Reference branch offset resistance in internal reference in $\Omega$ , format fd16; typical value 0 (calibrate if desired)                                                                      |

| 97  | FWD_EXT_REF_VAL       | Ħ                      | Value of reference resistor $R_{ref}$ in $\Omega$ , format fd16;<br>typical value for PT1000: 1k $\Omega$ =0x03E80000                                                                           |

| 98  | FWD_PT_INT_SLOPE      |                        | Internal sensor resistance slope in $(K/\Omega)^*$ Rref; format fd13; typical value 0x0029F000 (calibrate if desired)                                                                           |

| 99  | FWD_PT_INT_NOM        | Temperature measuremer | Internal sensor nominal resistance with fd 16; typical value 0x03C20000 (calibrate if desired)                                                                                                  |

| 100 | FWD_PTC_RATIO_INV     | Tempe                  | Nominal ratio of reference resistor to PT cold sensor resistance<br>at 0°C; format fd16;<br>typical value 1 = 0x00010000                                                                        |

| 101 | FWD_PTH_RATIO_INV     |                        | Nominal ratio of reference resistor to PT hot sensor resistance at 0 °C; format fd16; typical value 1 = 0x00010000                                                                              |

| 102 | FWD_HSC_CLOCK         | Phase                  | HSC clock in Hz, used as reference in the clock calibration<br>0x003D0900 = 4 MHz, 0x007A1200 = 8 MHz<br>0 is equivalent to 4 MHz                                                               |

| 103 | FWD_MH_RLS_DLY     |                                  | Nominal value for release delay; calculated only when FWD_MH_RLS_DLY_LIM ≠0                                                                                                                                                                                                                                                                          |

|-----|--------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 104 | FWD_PH_S_THRESHOLD |                                  | Absolute value of phase-shift threshold value. Cannot be a negative number, fd16 * $T_{\text{ref}}(\text{ns})$                                                                                                                                                                                                                                       |

| 105 | FWD_MH_RLS_DLY_LIM |                                  | Multihit release delay limits (min B1, B0. & max B3, B2.);<br>average is initial value; 1 LSB = 62.5 ns                                                                                                                                                                                                                                              |

| 106 | FWD_FW_CONFIG      |                                  | ScioSense firmware configuration register                                                                                                                                                                                                                                                                                                            |

| 107 | FWD_FW_RLS         |                                  | Boot loader release. 0xABCD7654 activates the bootloading process after start-up                                                                                                                                                                                                                                                                     |

| 108 | FWD_R_CD           |                                  | <ul> <li>Watchdog disable code</li> <li>Without ScioSense firmware, 0x48DBA399 disables the watchdog while any other code enables it.</li> <li>With ScioSense firmware, the watchdog can't be disabled, but 0x00000000 disables configuration restore after recall. Reset after POR should be applied.</li> <li>Proposed value 0x95659C6A</li> </ul> |

| 109 | FWD_IFC_CTRL       |                                  | Configuration data for CR_IFC_CTRL                                                                                                                                                                                                                                                                                                                   |

| 110 | FWD_GP_CTRL        |                                  | Configuration data for CR_GP_CTRL                                                                                                                                                                                                                                                                                                                    |

| 111 | FWD_USM_OPT        |                                  | Configuration data for CR_USM_OPT                                                                                                                                                                                                                                                                                                                    |

| 112 | FWD_IEH            |                                  | Configuration data for CR_IEH                                                                                                                                                                                                                                                                                                                        |

| 113 | FWD_CPM            | registers                        | Configuration data for CR_CPM                                                                                                                                                                                                                                                                                                                        |

| 114 | FWD_MRG_TS         | _                                | Configuration data for CR_MRG_TS                                                                                                                                                                                                                                                                                                                     |

| 115 | FWD_TPM            | guratio                          | Configuration data for CR_TPM                                                                                                                                                                                                                                                                                                                        |

| 116 | FWD_USM_PRC        | Initial values for configuration | Configuration data for <b>CR_USM_PRC</b> ;<br>ScioSense firmware interprets B3 as TOF_RATE;                                                                                                                                                                                                                                                          |

| 117 | FWD_USM_FRC        | value                            | Configuration data for CR_USM_FRC                                                                                                                                                                                                                                                                                                                    |

| 118 | FWD_USM_TOF        | Initial                          | Configuration data for CR_USM_TOF                                                                                                                                                                                                                                                                                                                    |

| 119 | FWD_USM_AM         |                                  | Configuration data for CR_USM_AM                                                                                                                                                                                                                                                                                                                     |

| 120 | FWD_TRIM1          |                                  | Configuration data for <b>CR_TRIM1</b> ;<br>Set to 0x94A0C46C                                                                                                                                                                                                                                                                                        |

| 121 | FWD_TRIM2          |                                  | Configuration data for <b>CR_TRIM2</b> ;<br>Set to 0x401100C7                                                                                                                                                                                                                                                                                        |

| 122 | FWD_TRIM3     |           | Configuration data for <b>CR_TRIM3</b> ;<br>Set to 0x00A7400F |                                                        |  |  |

|-----|---------------|-----------|---------------------------------------------------------------|--------------------------------------------------------|--|--|

| 123 | NOT USED      |           |                                                               |                                                        |  |  |

| 124 | FWD_R_FWD1_CS |           | Checksum firmware data 1                                      | These checksums are stored for comparison to values    |  |  |

| 125 | FWD_R_FWD2_CS | smu       | Checksum firmware data 2                                      | calculated by the chip.<br>Deviations in comparison    |  |  |

| 126 | FWD_R_FWU_CS  | Checksums | Checksum firmware code user                                   | cause checksum errors.<br>Can be calculated by the UFC |  |  |

| 127 | FWD_R_FWA_CS  | 0         | Checksum firmware code<br>ScioSense                           | Evaluation Software.                                   |  |  |

# 5.2 Parameters & Flags for General Operation Control

The most important register is *FWD\_FW\_CONFIG* (firmware configuration), which controls most options for firmware operation.

#### Table 2: Firmware data (FWD)

| Addr: 0 | x16A Cell: 106                | FWD_FW_  | FWD_FW_CONFIG (Firmware Configuration) |                                                                                                                                                                                                                        |  |  |  |

|---------|-------------------------------|----------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit     | Bit Name                      | Default  | Format                                 | Bit Description                                                                                                                                                                                                        |  |  |  |

| 7:0     | PWL_ADDR                      | 0b10     | UINT<br>[7:0]                          | (optional)<br>Start address of PWL coefficients table in FWD<br>(without leading address bit 8, which is always 1 in<br>FWD addresses) <sup>2</sup>                                                                    |  |  |  |

| 13:8    | PWL_EXP                       | 0b000001 | UINT<br>[5:0]                          | (optional)<br>Exponent of scaling factor for PWL coefficients: scale<br>up each value by 2 <sup>^</sup> ( <b>PWL_EXP</b> ) <sup>2</sup>                                                                                |  |  |  |

| 14      | NOT USED                      | 0b0      | BIT                                    | Set to zero                                                                                                                                                                                                            |  |  |  |

| 15      | BNR_FWCONF_PWL                | 0b0      | BIT                                    | Enable PWL calibration                                                                                                                                                                                                 |  |  |  |

| 16      | 16 BNR_FWCONF_2MAX<br>_NOZERO |          | BIT                                    | <ul><li>0: Set flow to zero when exceeding 2x maximum flow<br/>and signal error</li><li>1: Flow remains even when exceeding 2x maximum<br/>flow, but error flag is set</li></ul>                                       |  |  |  |

| 17      | BNR_FWCONF_FHL<br>_ZEROFLOW   | 060      | BIT                                    | <ul> <li>0: With FHL regulation active, disable zero flow state<br/>(always assume full flow as long as FHL is<br/>considered not ok)</li> <li>1: Apply zero flow state independently of FHL<br/>regulation</li> </ul> |  |  |  |

<sup>&</sup>lt;sup>2</sup> Generated by calibration engine

| 18    | BNR_FWCONF_FILTER           | 0b0  | BIT | Enable IIR filter for HSC factor and AM values                                                                                                                                                                                                                                     |

|-------|-----------------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19    | BNR_FWCONF_NOENF<br>_RECALL | 0b0  | BIT | Don't enforce recall setting (recall still happens as configured) 0: recall settings are enforced to 1 s, 5 s,10 min or 1 h                                                                                                                                                        |

| 20    | BNR_FWCONF_IND_RECALL0      | 0b0  | BIT | To be changed to 1 by FW after initialization due to recall; corresponds to bit 28, for constant checksums                                                                                                                                                                         |

| 21    | BNR_FWCONF_NO_PI_ERR        | 0b0  | BIT | <ul><li>0: Signal error on pulse interface as configured in bit</li><li>22</li><li>1: Never signal error on pulse interface</li></ul>                                                                                                                                              |

| 22    | BNR_FWCONF_PI_ERROR         | 0b0  | BIT | <ul><li>0: Don't signal no-water/hardware error as error on pulse interface</li><li>1: Also signal no-water/hardware error as error on pulse interface</li></ul>                                                                                                                   |

| 23    | BNR_FWCONF_ERR              | 0b0  | BIT | Activate average error counters<br>0: No average error counters<br>1: Average error counters active                                                                                                                                                                                |

| 25:24 | BNR_FWCONF_FHL              | 0600 | BIT | Configuration of FHL regulation methods<br>00: Method 1, fixed FHL<br>01: Method 2, consistency check against trusted FHL<br>10: Method 3, consistency check against trusted FHL<br>with offset time<br>11: Method 4, consistency check against special<br>configuration           |

| 26    | BNR_FWCONF_<br>FHL_RATIO    | 0b0  | BIT | Configuration for FHL regulation option B<br>0: Interpret FHL-values as fixed voltage<br>1: Interpret FHL-values as ratio to measured<br>amplitude                                                                                                                                 |

| 27    | BNR_FWCONF_VLIM             | 0b0  | BIT | 0: Disable control of speed of sound limits<br>1: Enable control of speed of sound limits                                                                                                                                                                                          |

| 28    | BNR_FWCONF_IND<br>_RECALL   | 060  | BIT | Activate recall initialisation, to be changed to 0 after<br>initialization due to recall<br>0: No recall initialization due or no initialization<br>configured<br>1: Initialization after recall<br>Note: for constant checksum generation set this to 1<br>(correlates to bit 20) |

| 29    | BNR_FWCONF_VOL              | 0b0  | BIT | Flow volume storage protection: flow volume is stored<br>in three pairs of RAM cells, such that a correction can<br>be applied. When all three data are different then an<br>error flag is raised.                                                                                 |

30

31

|                  |     |     | 0: Don't apply<br>1: Apply <sup>3</sup>                                                                                                                                     |

|------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BNR_FWCONF_TSENS | 0b0 | BIT | <ul><li>0: Use temperature value from flow meas. for calibration coefficients</li><li>1: Use temperature value from hot sensor meas. for calibration coefficients</li></ul> |

| BNR_FWCONF_ACAM  | 0b0 | BIT | 0: Apply ScioSense calibration method<br>1: Disable ScioSense calibration method                                                                                            |

CONTENTS PAGE

#### 5.3 Parameters for Hardware

The most convenient way to define and test the best hardware configuration is by using the ScioSense UFC Evaluation Software. From there the configuration data can be directly included into the firmware data file. With the right setting of the bootloader, the configuration will then be automatically loaded from the firmware data after a power-on reset.

A few remarks are necessary:

- The TOF rate is not stored in AS6031 configuration registers. The firmware uses B3 of cell 116 (*FWD\_USM\_PRC*) to define TOF rates above 1. TOF rate 0 is not permitted with unmodified ScioSense firmware.

- FHL values are not stored in AS6031 configuration registers. For FHL setting and regulation see section 7.

- With the ScioSense firmware the watchdog is always enabled. Cell 108 (*FWD\_R\_CD*), normally reserved for the watchdog disable code (0x48DBA399), has a different function.

- 0x0000000 in cell 108: watchdog always enabled, the firmware does not refresh the configuration and other permanent settings hourly. This is helpful during development, when the configuration under test is frequently varied. With this setting a reset should be applied after a power-on reset.

- 0x95659C6A in cell 0x108: recommended for production.

- One more configuration setting is enforced by the firmware, no matter what is written in CR\_MRG\_TS or FWD\_MRG\_TS: The checksum timer is always set to "hourly", such that every full hour a data recall is done. This restores the RAM part of the NVRAM memory. With cell 108 unequal 0x00000000, the firmware also restores the configurations and other permanent settings after recall. This is a safety measure in case RAM data was corrupted for any reason.

- In combination with ScioSense firmware the temperature measurement rate should be reduced, setting TM\_RATE > 1.

Note: ScioSense firmware sues GPIO5 and GPIO6 for diagnostics. They cannot be used otherwise.

<sup>&</sup>lt;sup>3</sup> Turn this bit off when the stored volume should be changed intentionally

#### 5.4 Parameters for Medium

Four parameters are used to describe the velocity of sound in pure water. They also define acceptable velocity limits for error handling. These parameters should not be changed when operating with water. For other media, please contact support.

| Cell | Variable Name     | Description<br>default value (if applicable)                                                                                                           |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74   | FWD_SOUND_VEL_MAX | Maximum of speed of sound in m/s<br>Default value for water 0x00061400<br>Format fd8                                                                   |

| 75   | FWD_1_BY_A        | Medium constant<br>Default value for water 0x002CA2E2                                                                                                  |

| 76   | FWD_CONST_C       | Medium constant<br>Default value for water 0x000F6C3A                                                                                                  |

| 77   | FWD_THETA_MAX     | B3/B2/B1: Temperature at maximum speed of sound in °C, format<br>fd8.<br>B0: minimal speed of sound, format fd5.<br>Default value for water 0x004A002B |

#### 5.5 Parameters for Calibration

All calibration parameters are generated by the calibration engine, see calibration engine user guide SC-001279-UG. Cells number 58 and 62 to 73 have to be adapted to individual spool pieces by 2-point calibration. Note that the address range for PWL coefficients can be selected through B0 of *FWD\_FW\_CONFIG* to optimize memory space needs. Usually only one calibration method is used, and the coefficients of the other one are free for other use. But it is also possible to have both types of calibrations stored and even enabled.

In step1 the parameters for a correct offset and in the following the speed of sound and temperature calculation are set. The distances with flow and with no flow describe the mechanical design. The SUMTOF offset is collected as a first measurement in 2-point calibration. The DIFTOF at high flow is used by the ScioSense algorithm only.

| Cell | Variable Name      | Function | Description<br>default value (if applicable)           |

|------|--------------------|----------|--------------------------------------------------------|

| 58   | RAM_TOF_OFFSET     |          | Offset time for SUMTOF in raw TDC units                |

| 59   | FWD_TOF_DIFF_CAL   |          | DIFTOF at high flow calibration point in raw TDC units |

| 60   | FWD_DIST_WITH_FLOW |          | Ultrasonic sound path length along flow in m (fd24)    |

| 61   | FWD_DIST_NO_FLOW   |          | Ultrasonic sound path length w/o flow in m (fd24)      |

#### Table 4: Firmware data step 1

In step 2 the DIFTOF is corrected in a linear manner, means by an offset O(T) and a scaling factor F(T). For the offset, the calibration engine output is base offsets O(TCx) and slopes (S\_O(TCx) for three temperatures and allows a precise offset interpolation:

$O(T) = O(TCx) + S_O(TCx)^*(TCx - TC_{measured}) / f_{ref}$

A simplified approach is using only one offset and slope factor for the complete temperature range.

The measured DIFTOF is then corrected by this offset.

For the scaling factor the output is similar, base factors F(TCx) and slopes (S\_F(TCx) for three temperatures and allows a precise offset interpolation:

$F(T) = F(TCx) + S_F(TCx)^*(TCx - TC_{measured}) / f_{ref}$

This scaling factor is applied to the finally calculated flow value.

#### Table 5: Firmware data linear correction<sup>4</sup>

| Cell | Variable Name         | -unction | Description<br>default value (if applicable)           |                 |                 |

|------|-----------------------|----------|--------------------------------------------------------|-----------------|-----------------|

| 54   | FWD_R_TEMP_TC1        | LL.      | Temperatures for linear calibration                    | on in °C        | 1 <sup>st</sup> |

| 55   | FWD_R_TEMP_TC2        |          | Format fd16                                            |                 | 2 <sup>nd</sup> |

| 56   | FWD_R_TEMP_TC3        |          |                                                        |                 | 3 <sup>rd</sup> |

| 57   | FWD_R_TEMP_TC4        |          |                                                        |                 | 4 <sup>th</sup> |

| 62   | FWD_R_ZERO_OFFSET_TC2 |          | Zero flow DIFTOF                                       | at TC2          |                 |

| 63   | FWD_R_ZERO_OFFSET_TC3 |          | O(TC)<br>Format fd32                                   | at TC3          |                 |

| 64   | FWD_R_ZERO_OFFSET_TC4 | -point)  |                                                        | at TC4          |                 |

| 65   | FWD_R_O_SLOPE_TC12    | ction (2 | Zero flow slope<br>S_O(TC)<br>Format fd16              | between TC1 and | TC2             |

| 66   | FWD_R_O_SLOPE_TC23    | correc   |                                                        | between TC2 and | TC3             |

| 67   | FWD_R_O_SLOPE_TC34    | Linear   |                                                        | between TC3 and | TC4             |

| 68   | FWD_R_F_SLOPE_TC12    |          | Proportionality factor slope<br>S_F(TC)<br>Format fd16 | between TC1 and | TC2             |

| 69   | FWD_R_F_SLOPE_TC23    |          |                                                        | between TC2 and | TC3             |

| 70   | FWD_R_F_SLOPE_TC34    |          |                                                        | between TC3 and | TC4             |

| 71   | FWD_R_F_OFFSET_TC2    |          | Proportionality factor<br>F(TC)                        | at TC2          |                 |

| 72   | FWD_R_F_OFFSET_TC3    |          | Format fd16                                            | at TC3          |                 |

| 73   | FWD_R_F_OFFSET_TC4    |          |                                                        | at TC4          |                 |

In advance to the flow calculation, a non-linear correction is applied to the DIFTOF. The choice is between the ScioSense proprietary method and a classical piecewise linear correction. The major choices are made in the firmware configuration register, see section 5.2.

PWL\_ADDR

(optional) Start address of PWL coefficients table in FWD (without leading address bit 8, which is always 1 in FWD addresses)

PWL\_EXP

(antional) Evenent of earling factor

(optional) Exponent of scaling factor for PWL coefficients: scale up each value by  $2^{PWL_{EXP}}$

<sup>4</sup> All those parameters are generated by the calibration engine. See User Guide UG403 for details. AS6031F1 Flow Firmware SC-001493-AN-2 / 2022-12-02 / Preliminary

- BNR\_FWCONF\_TSENS

- 0: Use temperature value from flow meas. for calibration coefficients

- 1: Use temperature value from hot sensor measurement for calibration

- BNR\_FWCONF\_PWL

- 0: Apply ScioSense calibration method

- 1: Enable PWL calibration method

All the non-linear correction coefficients will be generated by the calibration engine.

#### 5.6 Parameters for Zero Flow and Negative Flow Operation

In zero flow case, the ScioSense firmware can switch to an operation mode with reduced measurement rate and thus reduced current consumption. The following four parameters control this operation: The raw DIFTOF value in cell 94 is a limit for skipping calculation, with an absolute DIFTOF below that value no calculation is done and the flow is considered zero. In contrast, the limit in cell 95 is given as a flow, for example 0.5 l/h. If the actual averaged flow is below this value, the chip switches to zero flow operation: The TOF rate is increased by the factor defined on cell 89. In other words, the measurement rate is reduced by this factor. As soon as the average flow exceeds the value in cell 95, the chip switches back to full operation. Or, at the first single measurement (not averaged) which exceeds the value in cell 95 by a factor of 8, the chip also immediately returns to full operation. The flow averaging factor in cell 90 defines the range of averaging (actual averaging filter length is 16 times the value in cell 90, which must be a power of 2). This way the level of remaining noise after averaging can be controlled. A value of 0x00000010 = 16 is proposed, which means average flow is calculated as the arithmetic mean over the last 16 \* 16 = 256 measurements.