# **Datasheet**

DS000586

# **AS6501**

2-Channel Time-to-Digital Converter

v3-00 • 2020-May-19

# **Content Guide**

| Conten                   | t Guide 2                                           |

|--------------------------|-----------------------------------------------------|

| 1                        | General Description 3                               |

| 1.1<br>1.2<br>1.3        | Key Benefits & Features3Applications4Block Diagram4 |

| 2                        | Ordering Information 5                              |

| 3                        | Pin Assignment 6                                    |

| 3.1<br>3.2               | Pin Diagram                                         |

| 4                        | Absolute Maximum Ratings 9                          |

| 5                        | Recommended Operation Conditions10                  |

| 6                        | Typical Characteristics 12                          |

| 6.1<br>6.2               | Converter Characteristics                           |

| 6.3<br>6.4<br>6.5<br>6.6 | Reference Clock and Stop Input Requirements         |

| 6.4<br>6.5               | Reference Clock and Stop Input Requirements         |

| 8                                                    | Detailed Description3                                                         | 80                                     |

|------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8 | Time Measurements and Results                                                 | 32<br>33<br>35<br>37<br>40<br>44<br>46 |

|                                                      |                                                                               |                                        |

| 9                                                    | Application Information5                                                      | 2                                      |

| 9.1<br>9.2<br>9.3<br>9.4                             | Application Information                                                       | 52<br>52<br>55                         |

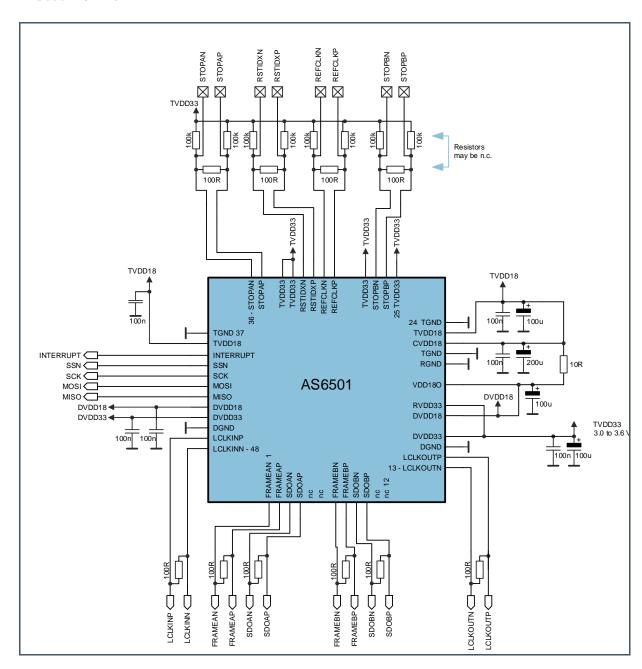

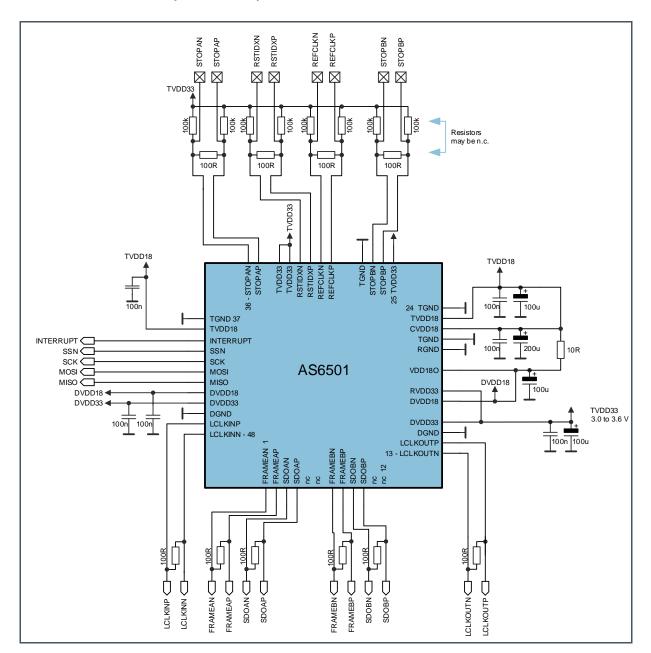

| 9.1<br>9.2<br>9.3                                    | Configuration Examples 5 Example C++ Code 5 Schematic 5                       | 52<br>52<br>55<br>56                   |

| 9.1<br>9.2<br>9.3<br>9.4                             | Configuration Examples 5 Example C++ Code 5 Schematic 5 External Components 5 | 52<br>55<br>56<br><b>6</b>             |

# 1 General Description

The AS6501 is a high performance time-to-digital converter (TDC) frontend device. Highest measurement performance and highest data throughput is achieved on two channels, each on with LVDS stop inputs and LVDS serial outputs. High configuration flexibility and unlimited measurement range cover many applications. They range from portable handheld laser range equipment to ambitious time-of-flight measurements of highest performance, as e.g. done in medical imaging applications.

AS6501 calculates all stop measurements inside, proportional to the applied reference clock. Combinations of best single shot accuracy of 10 ps with lowest pulse-to-pulse spacing < 5ns and maximum data throughput rate of 70 MSPS per stop input are possible.

# 1.1 Key Benefits & Features

The benefits and features of AS6501, 2-Channel Time-to-Digital Converter, are listed below:

Figure 1: Added Value of Using AS6501

| Benefits                                                                                                                                                                                         | Features                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Simple data post-processing thanks to calibrated results                                                                                                                                         | <ul> <li>2 stop channels with serial 20 ns pulse-to-pulse spacing and maximum 35 MSPS</li> <li>1 combined channel with 5 ns pulse-to-pulse spacing and maximum 70 MSPS</li> <li>Single shot accuracy 20 ps rms single shot resolution per channel or 10 ps rms with high resolution option</li> <li>Unlimited measuring range 0 s to 16 s</li> </ul> |

| <ul> <li>Event assignment thanks to reference clock index simplifies coincidence measurements</li> <li>Easy pulse width measurements</li> <li>High efficiency thanks high sample rate</li> </ul> | <ul> <li>Differential reference clock input 2 MHz to 12.5 MHz</li> <li>Inputs optional with LVDS (or CMOS level)</li> <li>LVDS serial output per channel</li> <li>16-stage FIFO per channel</li> <li>Automatic calibration to reference clock (no PLL or DLL)</li> <li>SPI compatible 4-wire interface for configuration</li> </ul>                  |

| <ul> <li>Compact design thanks to small package<br/>and low number of external components</li> <li>Reduced cooling thanks to low power<br/>consumption</li> </ul>                                | <ul> <li>Supply voltage 3.3 V</li> <li>Power dissipation 60 mW to 260 mW</li> <li>Standby current 60 µA</li> <li>QFP48 package (7 mm x 7 mm)</li> </ul>                                                                                                                                                                                              |

# 1.2 Applications

- Automated test equipment

- Laser range measurement

- Medical imaging

- Time-of-flight measurement

- Particle physics

- Lidar

# 1.3 Block Diagram

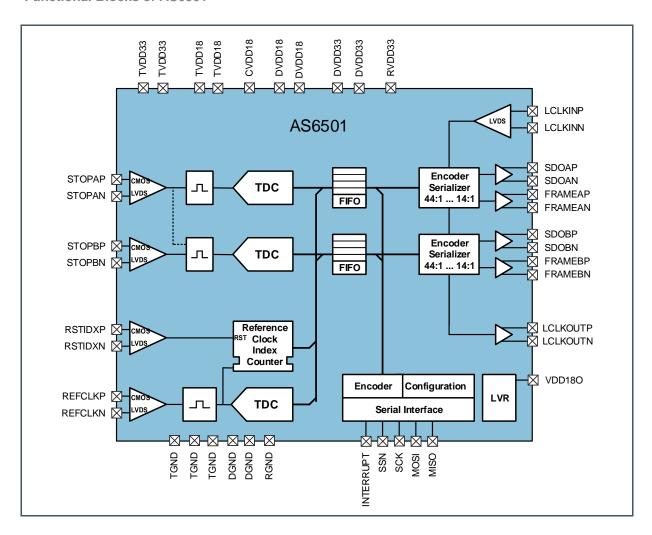

The functional blocks of this device are shown below:

Figure 2: Functional Blocks of AS6501

# 2 Ordering Information

| Ordering Code | Package | Marking | Delivery Form | Delivery Quantity |

|---------------|---------|---------|---------------|-------------------|

| AS6501-FLQM   | QFP48   | AS6501  | T&R           | 500 pcs/reel      |

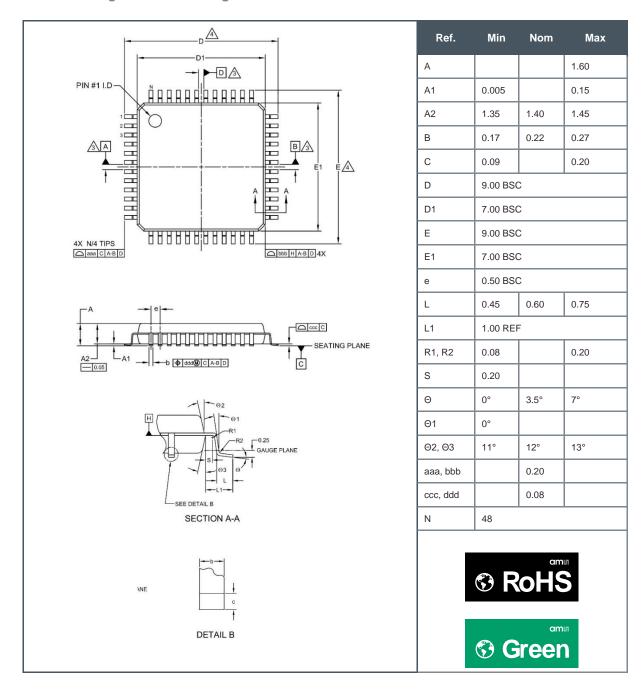

# 3 Pin Assignment

# 3.1 Pin Diagram

**Figure 3: AS6501 QFP48**

# 3.2 Pin Description

Figure 4: Pin Description of AS6501 QFP48

| Pin<br>Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                            | Not<br>Used |

|---------------|----------|-------------------------|--------------------------------------------------------|-------------|

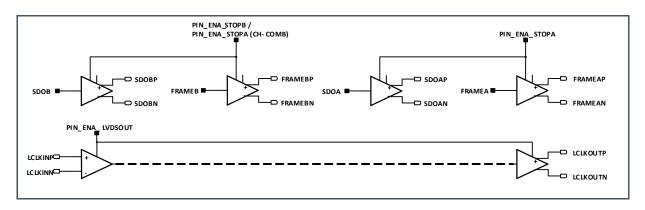

| 1             | FRAMEAN  | LVDS Output             | Negative frame signal of stop channel A                | Open        |

| 2             | FRAMEAP  | LVDS Output             | Positive frame signal of stop channel A                | Open        |

| 3             | SDOAN    | LVDS Output             | Negative serial data output of stop channel A          | Open        |

| 4             | SDOAP    | LVDS Output             | Positive serial data output of stop channel A          | Open        |

| 5, 6          | NC       |                         | Not Connected                                          | Open        |

| 7             | FRAMEBN  | LVDS Output             | Negative frame signal of stop channel B                | Open        |

| 8             | FRAMEBP  | LVDS Output             | Positive frame signal of stop channel B                | Open        |

| 9             | SDOBN    | LVDS Output             | Negative serial data output of stop channel B          | Open        |

| 10            | SDOBP    | LVDS Output             | Positive serial data output of stop channel B          | Open        |

| 11, 12        | NC       |                         | Not Connected                                          | Open        |

| 13            | LCLKOUTN | LVDS Output             | Negative serial clock output                           | Open        |

| 14            | LCLKOUTP | LVDS Output             | Positive serial clock output                           | Open        |

| 15            | DGND     | Power Supply            | Ground for digital and IO units                        |             |

| 16            | DVDD33   | Power Supply            | 3.3V supply for digital and IO units                   |             |

| 17            | DVDD18   | Power Supply            | 1.8V supply for digital and IO units                   |             |

| 18            | RVDD33   | Power Supply            | 3.3V supply for linear voltage regulator               |             |

| 19            | VDD18O   | Regulator<br>Output     | 1.8V supply for digital and IO units, regulator output |             |

| 20            | RGND     | Power Supply            | Ground for linear voltage regulator                    |             |

| 21            | TGND     | Power Supply            | Ground for TDC                                         |             |

| 22            | CVDD18   | Power Supply            | 1.8V positive supply for TDC                           |             |

| 23            | TVDD18   | Power Supply            | 1.8V positive supply for time front-end                |             |

| 24            | TGND     | Power Supply            | Ground for 1.8V time front-end supply                  |             |

| 25            | TVDD33   | Power Supply            | 3.3V positive supply for time front-end                |             |

| 26            | STOPBP   | CMOS/LVDS<br>Input      | Positive stop input for channel B                      | TVDD33      |

| 27            | STOPBN   | LVDS Input              | Negative stop input for channel B                      | TVDD33      |

| 28            | TVDD33   | Power Supply            | 3.3V positive supply for time front-end                |             |

|               |          |                         |                                                        |             |

| Pin<br>Number | Pin Name  | Pin Type <sup>(1)</sup> | Description                              | Not<br>Used |

|---------------|-----------|-------------------------|------------------------------------------|-------------|

| 29            | REFCLKP   | CMOS/LVDS<br>Input      | Positive clock signal of reference clock | TVDD33      |

| 30            | REFCLKN   | LVDS Input              | Negative clock signal of reference clock | TVDD33      |

| 31            | RSTIDXP   | CMOS/LVDS<br>Input      | Positive reference index reset signal    | TVDD33      |

| 32            | RSTIDXN   | LVDS Input              | Negative reference index reset signal    | TVDD33      |

| 33, 34        | TVDD33    | Power Supply            | 3.3V positive supply for time front-end  |             |

| 35            | STOPAP    | CMOS/LVDS<br>Input      | Positive stop input for channel A        | TVDD33      |

| 36            | STOPAN    | LVDS Input              | Negative stop input for channel A        | TVDD33      |

| 37            | TGND      | Power Supply            | Ground for TDC                           |             |

| 38            | TVDD18    | Power Supply            | 1.8V positive supply for time front-end  |             |

| 39            | INTERRUPT | LVTTL output            | SPI interrupt                            |             |

| 40            | SSN       | LVTTL Input             | SPI slave select not + interface reset   |             |

| 41            | SCK       | LVTTL Input             | SPI serial clock                         |             |

| 42            | MOSI      | LVTTL Input             | SPI serial data master out , slave In    |             |

| 43            | MISO      | LVTTL<br>Tristate       | SPI serial data master in, slave Out     |             |

| 44            | DVDD18    | Power Supply            | 1.8V supply for digital and IO units     |             |

| 45            | DVDD33    | Power Supply            | 3.3V supply for digital and IO units     |             |

| 46            | DGND      | Power Supply            | Ground for digital and IO units          |             |

| 47            | LCLKINP   | LVDS Input              | Positive serial clock in                 | DVDD33      |

| 48            | LCLKINN   | LVDS Input              | Negative serial clock in                 | DVDD33      |

# 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings of AS6501

| Symbol             | Parameter                          | Min  | Max            | Unit | Comments                                     |

|--------------------|------------------------------------|------|----------------|------|----------------------------------------------|

| Electrical Para    | meters                             |      |                |      |                                              |

| VDD33              | 3.3V Supply Voltage to Ground      | -0.5 | 4.0            | V    | Pin: DVDD33, TVDD33,<br>RVDD33               |

| VDD18              | 1.8V Supply Voltage to Ground      | -0.5 | 2.2            | V    | Pin: DVDD18, TVDD18,<br>CVDD18               |

|                    | Voltage between ground pins        | -0.3 | +0.3           | V    | Pin: DGND, TGND, RGND                        |

| V <sub>iLVDS</sub> | Voltage at differential input pins | -0.3 | VDD33 +<br>0.3 | V    | Pin: STOPA, STOPB,<br>REFCLK, RSTIDX, LCLKIN |

| Electrostatic D    | bischarge                          |      |                |      |                                              |

| ESD <sub>HBM</sub> | Electrostatic Discharge HBM        | ± ′  | 1000           | V    | JS-001-2014                                  |

| Temperature R      | langes and Storage Conditions      |      |                |      |                                              |

| TJ                 | Operating Junction Temperature     | -40  | 125            | °C   |                                              |

| T <sub>STRG</sub>  | Storage Temperature Range          | - 65 | 150            | °C   |                                              |

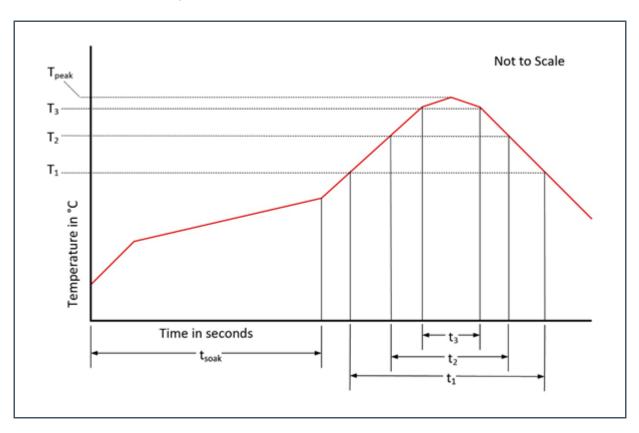

| T <sub>BODY</sub>  | Package Body Temperature           |      | 260            | °C   | IPC/JEDEC J-STD-020 (1)                      |

| RH <sub>NC</sub>   | Relative Humidity (non-condensing) | 5    | 85             | %    |                                              |

| MSL                | Moisture Sensitivity Level         |      | 3              |      | Maximum floor life time of 168h              |

<sup>(1)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100 % Sn)

# **5** Recommended Operation Conditions

Recommended operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Test conditions for guaranteed specification are expressly denoted.

Figure 6: Recommended Operation Conditions of AS6501

| Symbol               | Pin                          | Description                                                     | Min                           | Тур  | Max                                      | Unit |

|----------------------|------------------------------|-----------------------------------------------------------------|-------------------------------|------|------------------------------------------|------|

| Power-Sup            | ply                          |                                                                 |                               |      |                                          |      |

| VDD33                | DVDD33,<br>TVDD33,<br>RVDD33 | Supply Voltage                                                  | 2.4                           | 3.3  | 3.6                                      | V    |

| VDD18                | DVDD18,<br>TVDD18,<br>CVDD18 | Core Supply Voltage powered by integrated regulator, pin VDD18O | 1.7                           | 1.8  | 1.9                                      | V    |

| Temperatu            | re                           |                                                                 |                               |      |                                          |      |

| TA                   |                              | Operating free air temperature <sup>(1)</sup>                   | -40                           |      | 125                                      | °C   |

| Reference            | & Stop Inputs                |                                                                 |                               |      |                                          |      |

| V <sub>ID,LVDS</sub> |                              | LVDS Differential Input<br>Voltage                              | 200                           |      |                                          | mV   |

| VIC,LVDS             | STOPA, STOPB,<br>REFCLK,     | LVDS Common Mode Input<br>Voltage                               | 0.5 ×<br>V <sub>ID,LVDS</sub> | 1.25 | 2.2V to<br>0.5 ×<br>V <sub>ID,LVDS</sub> | V    |

| V <sub>IL,CMOS</sub> | — RSTIDX                     | CMOS Input Low Voltage                                          |                               |      | 0.4                                      | V    |

| V <sub>IH,CMOS</sub> |                              | CMOS Input High Voltage                                         | VDD33<br>- 0.4                |      |                                          | V    |

| SPI-Interfac         | ce                           |                                                                 |                               |      |                                          |      |

| VIL                  |                              | Digital Input LOW Voltage                                       |                               |      | 0.8                                      | V    |

| ViH                  | SCK, MOSI, SSN               | Digital Input HIGH Voltage                                      | 0.7 x<br>VDD33                |      |                                          | V    |

| CLOAD                | INTERRUPT,<br>MISO           | Load Capacitance to<br>Ground                                   |                               |      | 20                                       | pF   |

| LVDS-Inter           | face                         |                                                                 |                               |      |                                          |      |

| V <sub>ID,LVDS</sub> | LOLKINI                      | LVDS Differential Input<br>Voltage                              | 200                           |      |                                          | mV   |

| VIC,LVDS             | — LCLKIN                     | LVDS Common Mode Input<br>Voltage                               |                               | 1.25 |                                          | V    |

|                      |                              |                                                                 |                               |      |                                          |      |

| Symbol            | Pin                    | Description                                           | Min | Тур | Max | Unit |

|-------------------|------------------------|-------------------------------------------------------|-----|-----|-----|------|

| R <sub>TERM</sub> | SDOA, SDOB,<br>FRAMEA, | Differential Termination<br>Resistor for LVDS Outputs |     | 100 |     | Ohm  |

| CLOAD             | FRAMEB,<br>LCLKOUT     | Load Capacitance to Ground                            |     |     | 5   | pF   |

<sup>(1)</sup> Recommended Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Test conditions for guaranteed specification are explicitly denoted.

# **6** Typical Characteristics

The following test levels apply to all following characteristics:

Figure 7: Test Levels

| Test Level | Description                                                                          |

|------------|--------------------------------------------------------------------------------------|

| 1          | 100% production tested.                                                              |

| II         | 100% production tested at 25°C and guaranteed by design and characterization testing |

| III        | Parameter is guaranteed by design and characterization testing                       |

| IV         | Sample tested                                                                        |

| V          | Parameter is a typical value only.                                                   |

# 6.1 Converter Characteristics

General Conditions: VDD33 = 3.3 V; VDD18 = 1.8 V;  $T_A = 0$  °C to 80 °C.

Figure 8:

**Converter Characteristics**

| Symbol   | Description                    | Condition                  | TL | Min    | Тур | Max | Unit |

|----------|--------------------------------|----------------------------|----|--------|-----|-----|------|

| Accuracy | of Time Measurement            |                            |    |        |     |     |      |

| RMS      | Single-shot RMS                | High_Resolution = 0 (off)  |    |        | 20  | 30  |      |

|          | resolution                     | $High_Resolution = 1 (2x)$ | IV |        | 15  | 20  | ps   |

|          |                                | High_Resolution = $2(4x)$  |    |        | 10  | 15  |      |

| INL      | Integral non-linearity         |                            | IV |        |     | 20  | ps   |

| DNL      | Differential non-<br>linearity |                            | V  |        | 5   |     | ps   |

|          | No missing code                | At time quantization level | Ш  | Assure | ed  |     |      |

|          | Channel to channel isolation   | At same times measured     | IV |        | 20  | 100 | ps   |

|          | Offset error                   | High_Resolution = 0 (off)  |    |        | 100 |     |      |

|          |                                | $High_Resolution = 1 (2x)$ | V  |        | 150 |     | ps   |

|          |                                | High_Resolution = $2(4x)$  |    |        | 200 |     |      |

| Symbol   | Description                                                                       | Condition                                                                         | TL  | Min | Тур             | Max                 | Unit |

|----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----------------|---------------------|------|

|          | Offset error temperature drift                                                    | High_Resolution = 0 (off)<br>High_Resolution = 1 (2x)<br>High_Resolution = 2 (4x) | IV  |     | 0.5<br>1<br>1.5 | 3                   | ps/K |

| Switchin | g Performance                                                                     |                                                                                   |     |     |                 |                     |      |

| tconv    | Converter latency                                                                 | High_Resolution = 0 (off) High_Resolution = 1 (2x) High_Resolution = 2 (4x)       | III |     |                 | 20<br>50<br>100     | ns   |

|          | Peak conversion rate                                                              | High_Resolution = 0 (off) High_Resolution = 1 (2x) High_Resolution = 2 (4x)       | III |     |                 | 50<br>20<br>10      | MSPS |

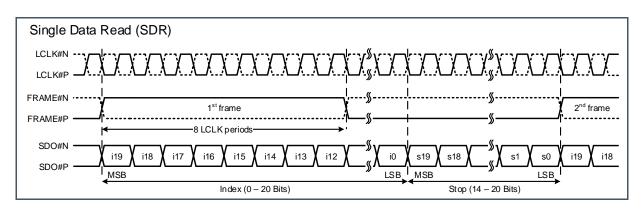

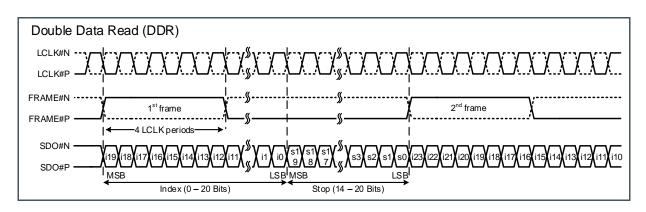

|          | Maximal read-out rate<br>SDR: LCLK=250MHz<br>DDR: LCLK=250MHz<br>SPI: SCK = 50MHz | Data bit width:<br>14-Bit<br>14-Bit<br>Opcode + 16-Bit                            | III |     |                 | 17.8<br>35.7<br>2.1 | MSPS |

|          | Maximal read-out rate<br>SDR: LCLK=250MHz<br>DDR: LCLK=250MHz<br>SPI: SCK = 50MHz | Data bit width:<br>44-Bit<br>44-Bit<br>Opcode + 48-Bit                            | III |     |                 | 5.6<br>11.3<br>0.9  | MSPS |

# 6.2 Power Supply Characteristics

General Conditions: VDD33 = 3.3 V; VDD18 = 1.8 V;  $T_A$  = 0 °C to 80 °C.

Figure 9:

**Power Supply Characteristics**

| Symbol      | Description                                                                    | Condition                                                                     | TL Min | Тур | Max | Unit |

|-------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------|-----|-----|------|

| Supply Volt | age                                                                            |                                                                               |        |     |     |      |

| tvDD180     | Delay from power-<br>up of RVDD33 to<br>TVDD18O,<br>CVDD18O,<br>DVDD18O stable | $C_{load} = 100 \ \mu F$                                                      | V      |     | 100 | ms   |

| Ртот,мім    | Minimum total power dissipation                                                | CMOS inputs and SPI read  freeclk = 5 MHz  conversion rate 1MSPS              | V      | 60  |     | mW   |

| Ртот,мах    | Maximum total power                                                            | LVDS inputs and outputs  freeclk = 10 MHz  fstopa,b = 50 MHz  flclk = 250 MHz | V      | 260 |     | mW   |

| Symbol                          | Description                         | Condition                   | TL Min | Тур | Max | Unit |

|---------------------------------|-------------------------------------|-----------------------------|--------|-----|-----|------|

| Detailed Cur                    | rent Consumption                    |                             |        |     |     |      |

| IDVDD18,REFCLK                  | Core current into REFCLK            | f <sub>REFCLK</sub> = 5 MHz | V      | 2   |     | mA   |

| DVDD18,STOP                     | Current per stop channel            | Stop rate = 0.5 MHz         | V      | 0.5 |     | mA   |

| ICVDD18                         | Current with activated TDC core     |                             | V      | 14  |     | mA   |

| IDVDD33,LVDS-IN ITVDD33,LVDS-IN | Current per LVDS input buffer       |                             | III    | 2   | 6   | mA   |

| IDVDD33,LVDS-<br>OUT            | Current per LVDS output buffer      | R <sub>TERM</sub> = 100 Ω   | III    | 5   | 10  | mA   |

| I <sub>DDQ</sub>                | Quiescent current mainly by IRVDD33 | LVDS inputs tied to VDD33   | II     | 60  | 100 | μΑ   |

| I <sub>LKG</sub>                | Input leakage current               | LVDS, CMOS, Digital         | II -5  |     | 1   | μΑ   |

|                                 |                                     |                             |        |     |     |      |

# 6.3 Reference Clock and Stop Input Requirements

General Conditions: VDD33 = 3.3 V; VDD18 = 1.8 V;  $T_A$  = 0 °C to 80 °C; VID = 200mV; VIC = 1.25 V; VIL = 0 V; VIH = 3.3 V

Figure 10: Clock and Input Characteristics

| Symbol                 | Description                        | Condition                                                                   | TL  | Min             | Тур         | Max                  | Unit |

|------------------------|------------------------------------|-----------------------------------------------------------------------------|-----|-----------------|-------------|----------------------|------|

| frefclk                | Reference clock frequency          | High_Resolution = 0 (off) High_Resolution = 1 (2x) High_Resolution = 2 (4x) | III | 2<br>2<br>2     | 5<br>5<br>5 | 12.5<br>12.5<br>10.0 | MHz  |

| TREFCLK                | Reference clock period             |                                                                             | III | 83              | 200         | 500                  | ns   |

|                        | Reference clock jitter             |                                                                             | V   |                 |             | 100                  | ps   |

|                        | Reference clock stability          | No requirement                                                              |     |                 |             |                      |      |

| t <sub>PWH</sub> ,stop | Minimum pulse width                | LVDS<br>CMOS                                                                | III | 2<br>10         |             |                      | ns   |

| tpps                   | Minimum pulse-to-<br>pulse spacing | High_Resolution = 0 (off) High_Resolution = 1 (2x) High_Resolution = 2 (4x) | III | 20<br>50<br>100 |             |                      | ns   |

| Symbol          | Description                                                           | Condition                                                             | TL  | Min | Тур | Max | Unit |

|-----------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|-----|------|

| tpps,cch        | Minimum pulse-to-<br>pulse spacing for a<br>single pair of pulses     | CHANNEL_COMBINE = 1                                                   | III | 5   |     |     | ns   |

| <b>t</b> su,RST | Setup Time from<br>RSTIDX to REFCLK                                   |                                                                       | Ш   | 5   |     |     | ns   |

| thd,RST         | Hold Time from RSTIDX to REFCLK                                       |                                                                       | Ш   | 5   |     |     | ns   |

| tpin_ena        | Pin Activation Time from configuration of PIN_ENA to valid data       | Pins: RSTIDX, REFCLK,<br>STOPA/B                                      | III | 200 |     |     | μs   |

| tpor            | Delay between power-on or initialization reset and next communication | Delay between power-on or initialization reset and next communication | III | 100 |     |     | μs   |

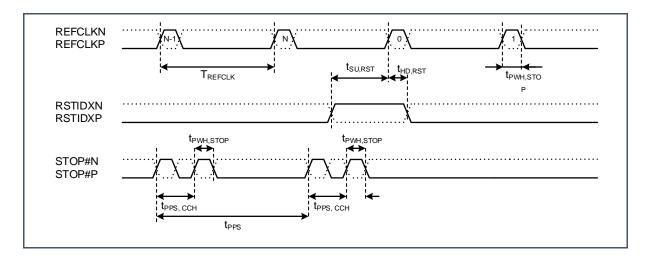

Figure 11: Timing Symbols and Parameters

# 6.4 LVDS Data Interface Characteristics

General Conditions: VDD33 = 3.3 V; VDD18 = 1.8 V; TA = 0 °C to 80 °C; VID = 200mV; VIC = 1.25 V

Figure 12: LVDS Interface Characteristics

| Symbol               | Description                                                              | Condition                                    | TL  | Min   | Тур    | Max   | Unit  |

|----------------------|--------------------------------------------------------------------------|----------------------------------------------|-----|-------|--------|-------|-------|

| Electrical C         | Characteristics                                                          |                                              |     |       |        |       |       |

| $V_{\text{OD,LVDS}}$ | LVDS differential output voltage                                         | $R_L = 100 \Omega$ ,<br>$C_L = 5 pF$         | Ш   | 200   |        |       | mV    |

| Voc,LVDS             | LVDS common<br>mode output<br>voltage                                    | $R_L = 100 \Omega$ ,<br>$C_L = 5 pF$         | III | 1.125 | 1.25   | 1.375 | V     |

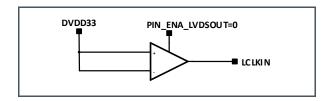

| t <sub>PIN_ENA</sub> | Pin activation time from configuration PIN_ENA_LVDS to valid data at pin | Pin:<br>LCLKIN, LCLKOUT,<br>SDOA/B, FRAMEA/B | III |       |        | 200   | μs    |

| Timing Cha           | aracteristics                                                            |                                              |     |       |        |       |       |

| tsync                | Synchronization latency                                                  | SDR<br>DDR                                   | III |       | 6<br>3 |       | Clock |

| t <sub>FRAME</sub>   | Frame length                                                             | SDR<br>DDR                                   | III |       | 8<br>4 |       | Clock |

| flclk                | LVDS clock<br>frequency<br>SDR/DDR                                       |                                              | III | 10    |        | 250   | MHz   |

|                      | LVDS clock duty cycle                                                    |                                              | III | 45    | 50     | 55    | %     |

|                      | Path delay LCLKIN<br>to LCLKOUT,<br>SDOA/B,<br>FRAMEA/B                  |                                              | III |       | 5      | 10    | ns    |

| t <sub>DV,LVDS</sub> | Data valid after active clock edge                                       | lvds_data_valid _adjust = 1                  | III |       | 0      |       | ns    |

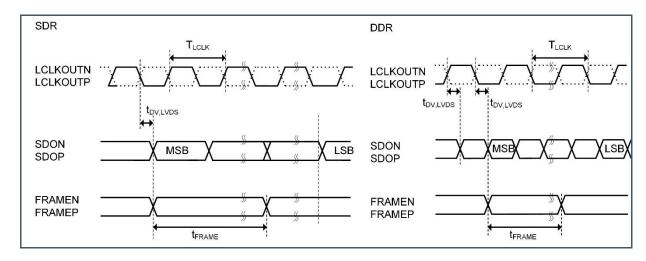

Figure 13: LVDS Timing Symbols and Parameters

## 6.5 Serial Communication Interface

General Conditions: VDD33 = 3.3 V; VDD18 = 1.8 V;  $T_A = 0$  °C to 80 °C; VIL = 0V; VIH = 3.3 V

Figure 14:

Serial Communication Interface Characteristics

| Symbol           | Description                                | Condition             | TL  | Min            | Тур | Max | Unit |

|------------------|--------------------------------------------|-----------------------|-----|----------------|-----|-----|------|

| Electrical (     | Characteristics                            |                       |     |                |     |     |      |

| Vol              | Digital Output LOW<br>Voltage              | I <sub>O</sub> = 2 mA | III |                |     | 0.3 | mV   |

| Vон              | Digital Output<br>HIGH Voltage             | I <sub>O</sub> = 2 mA | Ш   | DVDD33<br>-0.3 |     |     | mV   |

| Timing Cha       | aracteristics                              |                       |     |                |     |     |      |

| f <sub>SCK</sub> | Serial clock frequency                     | C <sub>L</sub> = 5 pF | III |                |     | 50  | MHz  |

| tpwh,sck         | Serial clock pulse width HI state          |                       | III | 10             |     |     | ns   |

| tpwl,sck         | Serial clock pulse width LO state          |                       | III | 10             |     |     | ns   |

| tpwh,ssn         | SSN pulse width<br>between write<br>cycles |                       | III | 10             |     |     | ns   |

| tsu,ssn          | SSN setup time after SCK falling           |                       | III | 20             |     |     | ns   |

| Symbol               | Description                         | Condition | TL | Min | Тур | Max | Unit |

|----------------------|-------------------------------------|-----------|----|-----|-----|-----|------|

| thd,ssn              | SSN hold time before SCK rising     |           | Ш  | 20  |     |     | ns   |

| t <sub>SU,MOSI</sub> | Data setup time prior to clock edge |           | Ш  | 5   |     |     | ns   |

| thd, mosi            | Data hold time after clock edge     |           | Ш  | 5   |     |     | ns   |

| t <sub>DV,MISO</sub> | Data valid after rising clock edge  |           | Ш  | 8   |     |     | ns   |

| tzx,miso             | HighZ to output time                |           | Ш  | 8   |     |     | ns   |

| txz,miso             | Output to HighZ time                |           | Ш  | 8   |     |     | ns   |

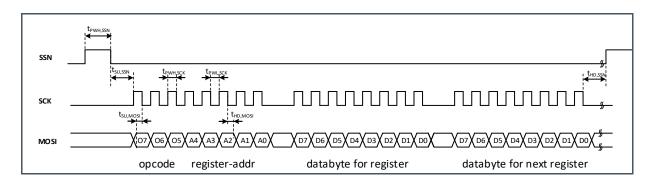

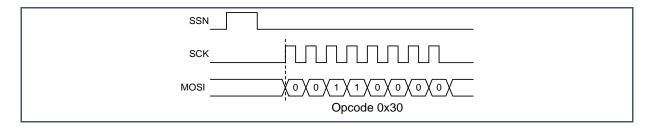

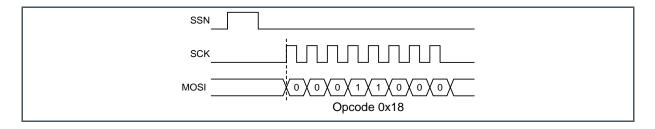

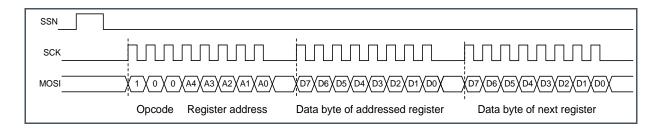

Figure 15: Write and Incremental Write

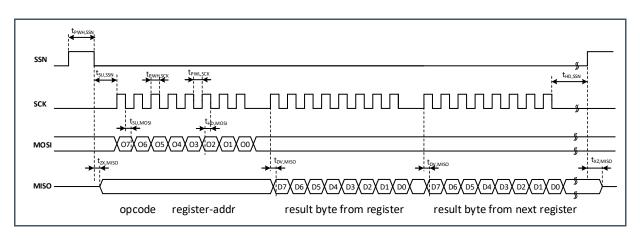

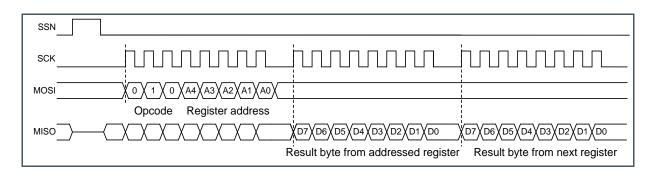

Figure 16: Read and Incremental Read

# 6.6 Typical Operating Characteristics

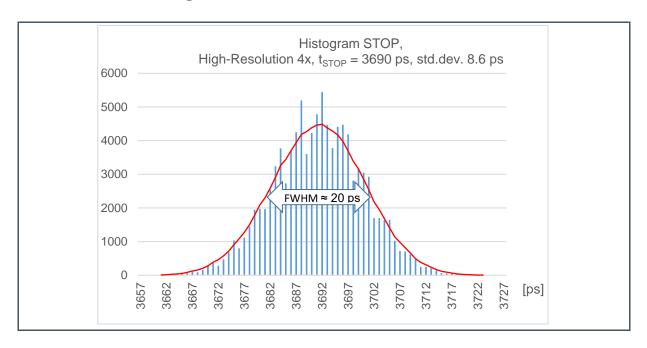

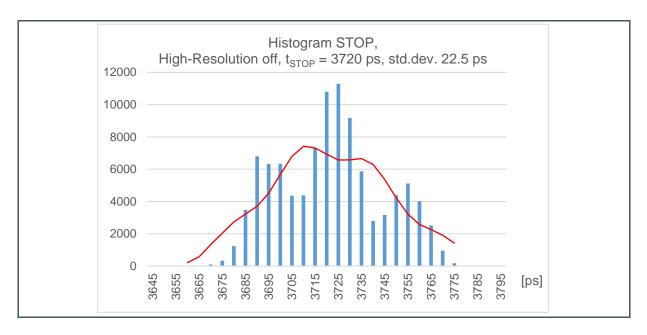

Figure 17: STOP, HIGHRES 4x, Histogram 100000 Values

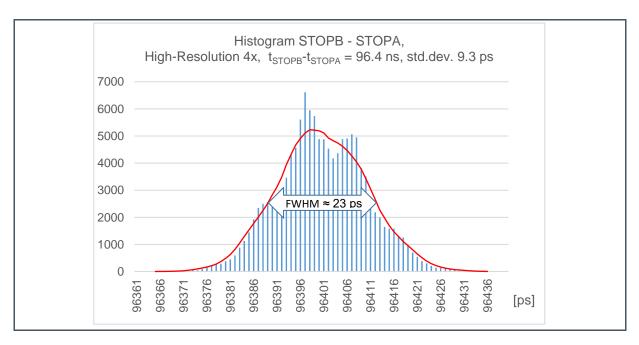

Figure 18: STOPB – STOPA, HIGHRES 4x, Histogram 100000 Values

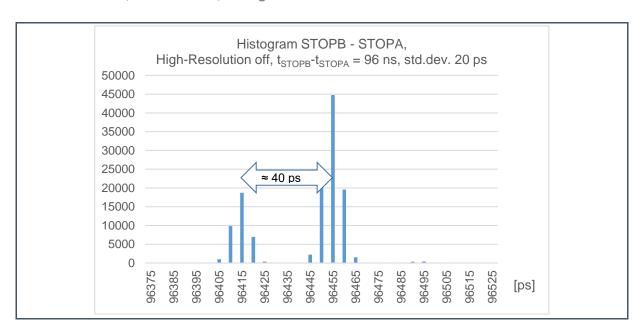

Figure 19: STOP – REFCLK, HIGHRES Off, Histogram 100000 Values

Figure 20: STOPB – STOPA, HIGHRES Off, Histogram 100000 Values

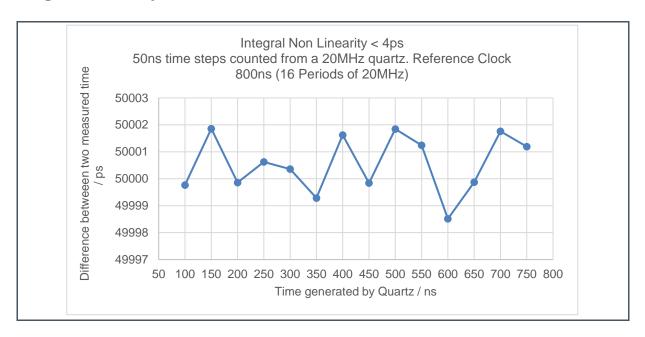

Figure 21: Integral Non-Linearity

# 7 Register Description

## 7.1 Register Overview

The configuration registers are organized in 17 addresses of one byte. All configuration registers are accessible via the SPI interface with the spiopc\_write\_config and spiopc\_read\_config. The result read registers are organized in 12 addresses of one byte. All result read registers are accessible via the SPI interface with spiopc\_read\_result. Users can read and write register individually or with an incremental access.

Figure 22: Configuration Register Overview

| Addr | Name  | <d7></d7>                      | <d6></d6>               | <d5></d5>           | <d4></d4>                 | <d3></d3>               | <d2></d2>             | <d1></d1>               | <d0></d0>             |

|------|-------|--------------------------------|-------------------------|---------------------|---------------------------|-------------------------|-----------------------|-------------------------|-----------------------|

| 0    | CFG0  | PIN_<br>ENA_<br>RSTIDX         | ENA_ (Ob) I.            |                     | PIN_<br>ENA_<br>REFCLK    | Fixed<br>value:<br>(0b) | PIN_<br>ENA_<br>STOPB | Fixed<br>value:<br>(0b) | PIN_<br>ENA_<br>STOPA |

| 1    | CFG1  | HIGH_<br>RESOLUT               | HIGH_ C<br>RESOLUTION C |                     | -                         | Fixed value: (0b)       | HIT_<br>ENA_<br>STOPB | Fixed value: (0b)       | HIT_<br>ENA_<br>STOPA |

| 2    | CFG2  | BLOCK<br>WISE_<br>FIFO<br>READ | WISE_ FIFO_ D           |                     | STOP_DAT<br>WIDTH         | A_BIT                   | A_BIT REF_INDE        |                         | DTH                   |

| 3    | CFG3  | REFCLK_                        | DIVISIONS (Lo           | wer byte)           |                           |                         |                       |                         |                       |

| 4    | CFG4  | REFCLK_                        | DIVISIONS (Mi           | ddle byte)          |                           |                         |                       |                         |                       |

| 5    | CFG5  | Fixed valu                     | e: (0000b)              |                     |                           | REFCLK                  | _DIVISIONS            | (Upper bit              | s)                    |

| 6    | CFG6  | Fixed valu                     | e: (110b)               |                     | LVDS_<br>TEST_<br>PATTERN | Fixed val               | ue: (0000b)           |                         |                       |

| 7    | CFG7  | Fixed valu                     | e: (01b)                | LVDS_DATA<br>ADJUST | A_VALID_                  | Fixed Val               | ue: (0011b)           |                         |                       |

| 8    | CFG8  | Fixed valu                     | e: (10100001b)          |                     |                           |                         |                       |                         |                       |

| 9    | CFG9  | Fixed valu                     | e: (00010011b)          |                     |                           |                         |                       |                         |                       |

| 10   | CFG10 | Fixed valu                     | e: (0000000b)           |                     |                           |                         |                       |                         |                       |

| 11   | CFG11 | Fixed valu                     | e: (00001010b)          |                     |                           |                         |                       |                         |                       |

| 12   | CFG12 | Fixed valu                     | e: (11001100b)          |                     |                           |                         |                       |                         |                       |

| 13   | CFG13 | Fixed valu                     | e: (11001100b)          |                     |                           |                         |                       |                         |                       |

| 14   | CFG14 | Fixed valu                     | e: (11110001b)          |                     |                           |                         |                       |                         |                       |

| 15   | CFG15 | Fixed valu                     | e: (01111101b)          |                     |                           |                         |                       |                         |                       |

| 16   | CFG16 | Fixed valu                     | e: (00000b)             |                     |                           |                         | CMOS_<br>INPUT        | Fixed val               | ue: (00b)             |

All register are read/write with 0 as default value, besides registers 13 and 14 with 5 as default value. The fixed values are assigned by **ScioSense**: Unless otherwise suggested, they should be set as shown in this table.

Figure 23: Result Register Overview

| Addr     | Name            | <d7></d7>                         |

|----------|-----------------|-----------------------------------|

| 0 to 7   |                 | n.c.                              |

| 8        |                 | REFERENCE INDEX CHANNEL A BYTE #3 |

| 9        |                 | REFERENCE INDEX CHANNEL A BYTE #2 |

| 10       | —<br>— CHANNELA | REFERENCE INDEX CHANNEL A BYTE #1 |

| 11       | — CHANNELA      | STOP RESULT CHANNEL A BYTE #3     |

| 12       |                 | STOP RESULT CHANNEL A BYTE #2     |

| 13       |                 | STOP RESULT CHANNEL A BYTE #1     |

| 14 to 19 |                 | n.c.                              |

| 20       |                 | REFERENCE INDEX CHANNEL B BYTE #3 |

| 21       | _               | REFERENCE INDEX CHANNEL B BYTE #2 |

| 22       | CHANNELD        | REFERENCE INDEX CHANNEL B BYTE #1 |

| 23       | — CHANNELB      | STOP RESULT CHANNEL B BYTE #3     |

| 24       |                 | STOP RESULT CHANNEL B BYTE #2     |

| 25       | _               | STOP RESULT CHANNEL B BYTE #1     |

# 7.2 Detailed Register Description

## 7.2.1 CFG0 Register (Address 0)

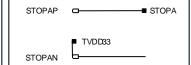

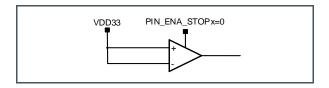

The PIN\_ENA registers activate the LVDS input or output drivers of the related pins. Main purpose of PIN\_ENA is cutting of current consumption of differential LVDS buffers to nearly zero. But also with CMOS input levels the pins have to be activated accordingly. Unused inputs has to be tied to VDD33.

Figure 24: CFG0 Register

| Addr | Addr: 0           |              | CFG0        |                                                                                                    |  |  |  |

|------|-------------------|--------------|-------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Bit  | Bit Name          | De-<br>fault | Ac-<br>cess | Bit Description                                                                                    |  |  |  |

| 0    | PIN_ENA_<br>STOPA | 0            | RW          | Activation on stop event input pin STOPA 0:= Stop input pins not active 1:= Stop input pins active |  |  |  |

| 1    | Fixed value:      | 0            | RW          | (0b)                                                                                               |  |  |  |

| Addr | r: 0                 | CFG          | )           |                                                                                                                                                              |

|------|----------------------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Bit Name             | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                              |

| 2    | PIN_ENA_<br>STOPB    | 0            | RW          | Activation on stop event input pin STOPB  0:= Stop input pins not active  1:= Stop input pins active                                                         |

| 3    | Fixed value:         | 0            | RW          | (0b)                                                                                                                                                         |

| 4    | PIN_ENA_<br>REFCLK   | 0            | RW          | 0:= REFCLK input pins not active 1:= REFCLK input pins active                                                                                                |

| 5    | PIN_ENA_<br>LVDS_OUT | 0            | RW          | 0:= All LDVS output pins disabled 1:= Activation of LCLK and LCLKOUT pins. Activation of SDOA/B and FRAMEA/B, depends further on CHANNEL_COMBINE and PIN_ENA |

| 6    | Fixed value:         | 0            | RW          | (0b)                                                                                                                                                         |

| 7    | PIN_ENA_<br>RSTIDX   | 0            | RW          | 0:= Deactivation of reference clock index counter reset pin 1:= Activation of reference clock index counter reset pin                                        |

## 7.2.2 CFG1 Register (Address 1)

Figure 25: CFG1 Register

| Addr | :1                  | CFG1         |             |                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------------------|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Bit Name            | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                                                                                                                                                                                                            |

| 0    | HIT_ENA_<br>STOPA   | 0            | RW          | 0:= Stop events are internally rejected. The pin enabling of STOPA is not affected. 1:= Stop events are internally accepted and processed. Normal working condition                                                                                                                                                                                                                                        |

| 1    | Fixed value:        | 0            | RW          | (0b)                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2    | HIT_ENA_<br>STOPB   | 0            | RW          | 0:= Stop events are internally rejected. The pin enabling of STOPB is not affected. 1:= Stop events are internally accepted and processed. Normal working condition                                                                                                                                                                                                                                        |

| 3    | Fixed value:        | 0            | RW          | (0b)                                                                                                                                                                                                                                                                                                                                                                                                       |

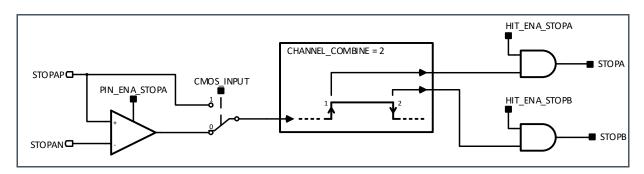

| 4, 5 | CHANNEL_<br>COMBINE | 0            | RW          | The two stop channels may be combined for improved pulse pair resolution or higher conversion rate.  00b := Normal operation with two independent stop channels 01b := "Pulse distance"  Stop events at STOPA are measured alternatingly by stop channels A & B  10b := "Pulse width"  The rising edges at STOPA are measured by stop channel A, the falling edges at STOPA are measured by stop channel B |

| Addr: 1 |                     | CFG1         |             |                                                                                                                                                                                                                                                                                                               |

|---------|---------------------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name            | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                                                                                                               |

| 6, 7    | HIGH_<br>RESOLUTION | 0            | RW          | A stop event is internally delayed, measured several times and summed up in order to one result to increase the time resolution.  00b := 0 (Off): standard resolution with minimal pulse-to-pulse spacing.  01b := 1 (2x): A stop event is measured twice  10b := 2 (4x): A stop event is measured four times |

## 7.2.3 CFG2 Register (Address 2)

Figure 26: CFG2 Register

| Addr: 2 |                           | CFG2         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------|---------------------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit     | Bit Name                  | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| [2:0]   | REF_INDEX_<br>BITWIDTH    | 0            | RW          | Bit width of reference clock index in LVDS output (not applicable to SPI data readout).  000b := 0 bit, no data out  001b := 2 bits  010b := 4 bits  011b := 8 bits  100b := 16 bits  101b := 24 bits  110b := 6 bits  111b := 12 bits                                                                                                                                                                                              |  |

| 3, 4    | STOP_DATA_<br>BITWIDTH    | 0            | RW          | Bit width of the stop result in LVDS output. Bit width should be sufficient to represent the REFCLK_DIVISIONS configuration value (not applicable to SPI data readout).  00b := 14 Bits → max of REFCLK_DIVISIONS = 2 <sup>14</sup> -1  01b := 16 Bits → max of REFCLK_DIVISIONS = 2 <sup>16</sup> -1  10b := 18 Bits → max of REFCLK_DIVISIONS = 2 <sup>18</sup> -1  11b := 20 Bits → max of REFCLK_DIVISIONS = 2 <sup>20</sup> -1 |  |

| 5       | LVDS_DOUBLE_<br>DATA_RATE | 0            | RW          | 0:= Single Data Read (SDR): The LVDS data clocked out on rising edges of LCLK-OUT  1:= Double Data Read (DDR): The LVDS data are clocked on both edges of LCLK-OUT                                                                                                                                                                                                                                                                  |  |

| Addr: | Addr: 2                 |              | CFG2        |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------|-------------------------|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit   | Bit Name                | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

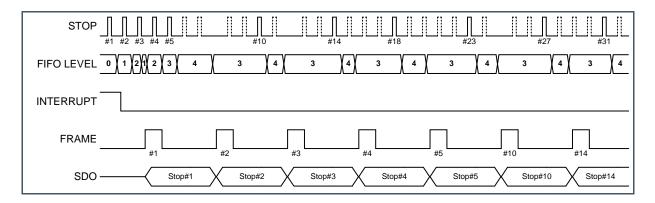

| 6     | COMMON_<br>FIFO_READ    | 0            | RW          | 0:= Off LVDS: Operation with two independent stop channels SPI: INTERUPT pin is set to zero, as soon as one FIFOs does have a value.OFF. 1:= On LVDS: All active frame pins are set simultaneous as soon as all related FIFOs have values. SPI: INTERUPT pin is set to zero, as soon as all active FIFOs have value. In combination with BLOCKWISE_READ this option guaranties successive measurements in parallel on all stop channels |  |

| 7     | BLOCKWISE_<br>FIFO_READ | 0            | RW          | 0:= OFF, Operation with standard FIFO function 1:= Data output (LVDS or SPI) is not started before a channel FIFO is full. Once FIFO is full, measurement is not restarted before FIFO is completely read-out. This option guaranties successive measurements at high stop event rate or slow read-out speeds (e.g. SPI)                                                                                                                |  |

## 7.2.4 CFG3, CFG4, CFG5 Registers (Addresses 3 to 5)

These registers combine for a 20-bit value.

Figure 27: CFG3, CFG4, CFG5 Registers

| Addr: 3 |                                   | CFGRG3       |             |                                                                                                                                                                                                                         |

|---------|-----------------------------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name                          | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                         |

| 0 to 7  | REFCLK_DIVISIONS<br>Lower 8 bits  | 0            | RW          | Defines a LSB at the output interface as fraction of the reference clock period. The most convenient way is applying a LSB of 1ps by configuring REFCLK_DIVISIONS to the picosecond value of the reference clock period |

| Addr: 4 | CFGRG4                            |              |             |                                                                                                                                                                                                                         |

| 0 to 7  | REFCLK_DIVISIONS<br>Middle 8 bits | 0            | RW          | See above                                                                                                                                                                                                               |

| Addr: 5 |                                   | CFGR         | G5          |                                                                                                                                                                                                                         |

| 0 to 3  | REFCLK_DIVISIONS<br>High 4 bits   | 0            | RW          | See above                                                                                                                                                                                                               |

| 4 to 7  | Fixed value:                      | 0            | RW          | (0000b)                                                                                                                                                                                                                 |

## 7.2.5 CFG6 Register (Address 6)

Figure 28: CFG6 Register

| Addr: 6 | Addr: 6               |              | CFG6        |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------|-----------------------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit     | Bit Name              | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 0 to 3  | Fixed value:          | 0            | RW          | (0000b)                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 4       | LVDS_TEST_<br>PATTERN | 0            | RW          | 0:= Normal operation of LVDS outputs 1:= LVDS interface continuously outputs the following test patterns. All stop events are ignored.  Reference index = 1111000011001100101010101011110000bin (=15781034dec) Stop result = 00001010101010111110000bin (=699632dec) Depending on the configuration of the output format width (REF_INDEX_BITWIDTH, STOP_DATA_BITWIDTH) only the corresponding lower bits are transmitted |  |

| 5 to 7  | Fixed value:          | 0            | RW          | (000b)                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

### 7.2.6 CFG7 Register (Address 7)

Figure 29: CFG7 Register

| Addr: 7 |                            | CFG7         | CFG7        |                                                                                                                               |  |

|---------|----------------------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Bit     | Bit Name                   | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                               |  |

| 0 to 3  | Fixed value:               | 0            | RW          | (0000b)                                                                                                                       |  |

| 4, 5    | LVDS_DATA_VALID_<br>ADJUST | 0            | RW          | Adjustment of the data valid time at the LVDS output interface.  00b := - 160 ps  01b := 0 ps  10b := +160 ps  11b := +320 ps |  |

| 6, 7    | Fixed value:               | 0            | RW          | (00b)                                                                                                                         |  |

## 7.2.7 CFG8 to CFG15 Register (Addresses 8 to 15)

For registers 8 to 15 use the default fixed values as shown in the Register Overview.

### 7.2.8 CFG16 Register (Address 16)

Figure 30: CFG16 Register

| Addr: 16 |              | CFG1         | 6           |                                                                                                                                                                                                                                                         |

|----------|--------------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Bit Name     | De-<br>fault | Ac-<br>cess | Bit Description                                                                                                                                                                                                                                         |

| 0, 1     | Fixed value: | 0            | RW          | (00b)                                                                                                                                                                                                                                                   |

| 2        | CMOS_INPUT   | 0            | RW          | Input voltage levels of STOPA and STOPB, REFCLK, RSTIDX are selected as CMOS or LVDS 0:= Differential LVDS input level. 1:= Single ended CMOS input level Also with CMOS input level the pins have to be activated with according PIN_ENA-configuration |

| 3 to 7   | Fixed value: | 0            | RW          | (00000b)                                                                                                                                                                                                                                                |

### 7.2.9 CHANNELA Result Register (Addresses 8 to 13)

ChannelA register is made of 6 bytes. Three bytes for the reference index REFID, three bytes for the time stamp:

Figure 31: CHANNELA Register

| Address | Name   | Description                 | Format                                        |  |  |

|---------|--------|-----------------------------|-----------------------------------------------|--|--|

| 8       |        | REFERENCE INDEX CH1 BYTE #3 |                                               |  |  |

| 9       | REFID1 | REFERENCE INDEX CH1 BYTE #2 | $REFID = 2^{16}xBYTE#3 + 2^8xBYTE#2 + BYTE#1$ |  |  |

| 10      |        | REFERENCE INDEX CH1 BYTE #1 |                                               |  |  |

| 11      |        | STOP RESULT CH1 BYTE #3     |                                               |  |  |

| 12      | TSTOPA | STOP RESULT CH1 BYTE #2     | $TSTOP = 2^{16}xBYTE#3 + 2^8xBYTE#2 + BYTE#1$ |  |  |

| 13      |        | STOP RESULT CH1 BYTE #1     |                                               |  |  |

REFID is the reference index of the preceding reference clock edge.

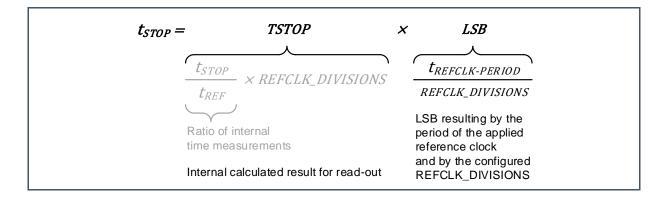

TSTOP is the ratio of the internal measured times of  $t_{STOP}$  over  $t_{REF}$  scaled by the configured REFCLK\_DIVISONS. For details see section Time Measurements and Results.

### 7.2.10 CHANNELB Result Register (Addresses 20 to 25)

ChannelA register is made of 6 bytes. Three bytes for the reference index REFID, three bytes for the time stamp:

Figure 32: CHANNELB Register

| Address | Name   | Description                 | Header row left aligned                                           |

|---------|--------|-----------------------------|-------------------------------------------------------------------|

| 20      |        | REFERENCE INDEX CH3 BYTE #3 |                                                                   |

| 21      | REFID3 | REFERENCE INDEX CH3 BYTE #2 | $REFID = 2^{16} \times BYTE#3 + 2^{8} \times BYTE#2 + BYTE#1$     |

| 22      |        | REFERENCE INDEX CH3 BYTE #1 |                                                                   |

| 23      |        | STOP RESULT CH3 BYTE #3     |                                                                   |

| 24      | TSTOPB | STOP RESULT CH3 BYTE #2     | TSTOP = 2 <sup>16</sup> xBYTE#3 + 2 <sup>8</sup> xBYTE#2 + BYTE#1 |

| 25      |        | STOP RESULT CH3 BYTE #1     |                                                                   |

REFID is the reference index of the preceding reference clock edge.

TSTOP is the measured time as ratio of the internal measured times of  $t_{\text{STOP}}$  over  $t_{\text{REF}}$  scaled by the configured REFCLK\_DIVISONS. For details see section Time Measurements and Results.

# 8 Detailed Description

### 8.1 Time Measurements and Results

#### 8.1.1 Measurements of AS6501

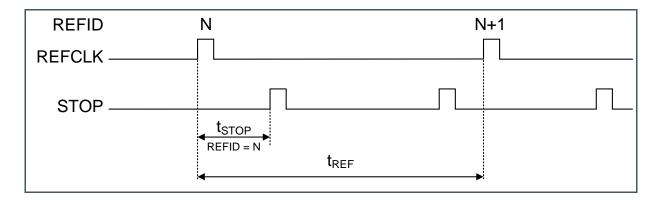

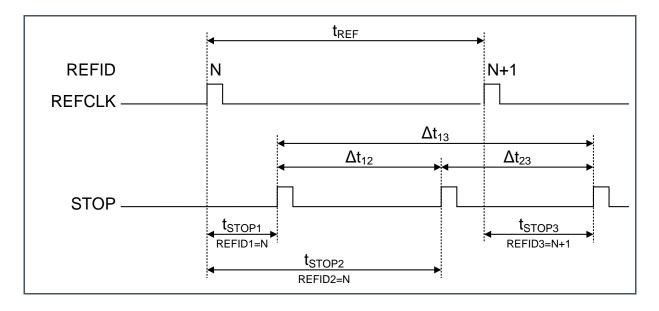

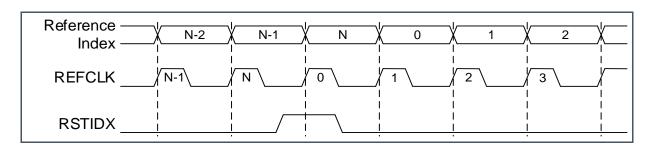

The reference clock is the framework for all time measurements. The clock pulses are measured continuously by the TDC as time reference point for stop pulses and as internal reference period. The measurement of the stop events always refers to the preceding reference clock. Additionally, the reference clock is counted continuously and the actual count is assigned as reference index to a stop pulse.

- tref is the internal TDC measurement of the reference clock period

- tstop is the internal TDC measurement of a stop to the preceding reference clock

- REFID is the index of reference period where the measured stop occurred

Figure 33: AS6501 Time Measurement

### 8.1.2 Output Results

Each stop generates a dataset that consists of two values TSTOP and REFID:

REFID is the reference index of the preceding reference clock pulse to TSTOP. The reference index is necessary to indicate the relationship of stop pulses that belong to different reference clock periods. The maximum length of the reference index is 20 bits.

TSTOP is the ratio of the internal measured times of  $t_{STOP}$  over  $t_{REF}$  scaled by the configured REFCLK\_DIVISONS. The readout result TSTOP is always less than configured REFCLK\_DIVISONS. The resulting LSB at the output interface should be chosen much lower than the single shot resolution of AS6501. For details, see chapter Coding of Results. Suitable values are e.g. 1 ps, 5 ps or 10 ps.

Figure 34: Time Calculation

#### 8.1.3 Calculation of Time Differences

The results of the AS6501 are the time intervals from stop event pulses to the preceding reference clock pulses. In many applications, the time difference between stop event pulses is desired. This happens e.g. in case of a quartz as a reference clock. Depending on the application and the measurement setup, several approaches are possible to calculate the time between two stops in the connected microprocessor or FPGA.

Figure 35: Calculating Time Differences

#### **GENERAL APPROACH**

On the output interface, either SPI or LVDS, both data REFID and TSTOP are available. With these data, it is possible to calculate time differences between stops. The maximum time difference depends on the bit width of the reference index (see also chapter Maximum Time Differences).

$\Delta t_{13} = (TSTOP3 - TSTOP1) + (REFID3 - REFID1) * REFCLK_DIVISIONS$

In two special cases it is not necessary to readout the REFID:

#### STOPS IN THE SAME REFERENCE CLOCK PERIOD

In applications where stops occur always in the same reference period, it is not necessary to read out the reference index. It is sufficient to read out just the stop results and to calculate the difference:

$\Delta t_{12} = TSTOP2 - TSTOP1$

if REFID2 = REFID1

#### TIME DIFFERENCE SMALLER THAN REFERENCE CLOCK

In applications where the measured time difference  $\Delta t$  is always smaller than the reference clock period TREF but not necessarily in the same reference clock period, it is often sufficient to read out just the stop results without the reference index by distinguishing positive and negative time difference:

$\Delta t_{23} = (TSTOP3 - TSTOP2)$

if TSTOP3 - TSTOP2 > 0

$\Delta t_{23} = (TSTOP3 - TSTOP2) + REFCLK_DIVISIONS$

if TSTOP3 – TSTOP2 < 0

### 8.2 Resolution

#### 8.2.1 RMS-Resolution versus Effective Resolution

The RMS resolution of a TDC is the root-mean-square-value of a set of single shot time measurements. TDC do not have an obvious full scale definition, as the time they are measuring is unlimited. Therefore, the definition of an effective resolution in number of bits likewise in ADC is not feasible.

#### 8.2.2 High Resolution

For achieving best single-shot RMS resolution, AS6501 offers a complete integrated solution. During the initial sampling, the stop event is internally delayed and sampled again, after the first sample was stored in the FIFO. All samples of one stop event are averaged inside of the AS6501 and occur as one result with lower conversion noise at the output interface. With HIGH\_RESOLUTION it is possible to configure internal 2 or 4 samples of one event. Due of the internal delay and the multiple samples the conversion latency t<sub>conv</sub> and the pulse-to-pulse spacing t<sub>PPS</sub> increase as well as the maximum FIFO\_DEPTH decreases. In order to compensate these drawbacks, it is possible to use HIGH\_RESOLUTION with both CHANNEL\_COMBINATION modes and to achieve the excellent pulse-to-pulse spacing of channel combination mode, doubled FIFO depth per stop input and higher resolution.

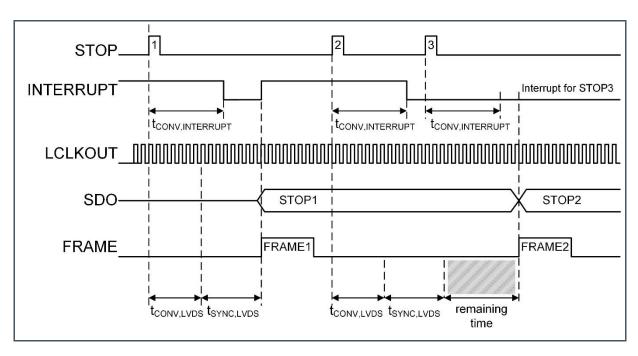

## 8.3 Combining Two Stop Channels

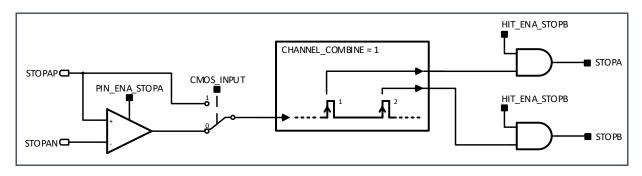

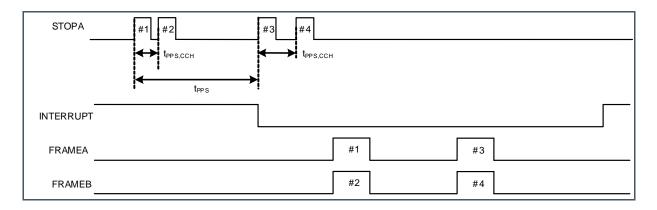

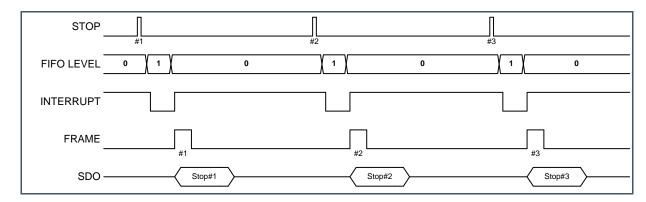

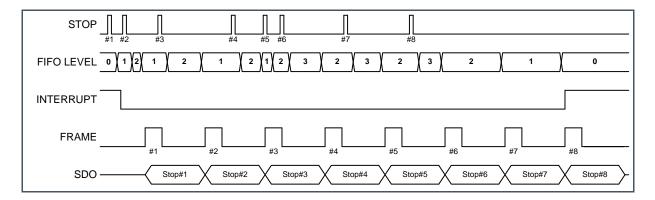

### 8.3.1 Channel Combination for Low Pulse-to-Pulse Spacing

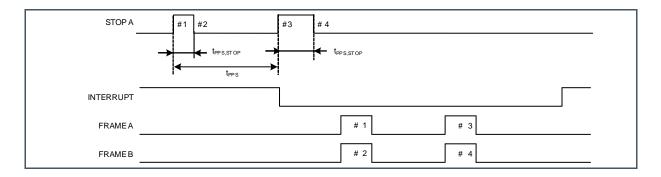

With CHANNEL\_COMBINE set to "PULSE\_SPACING", the two stop channels A & B are connected to one input pin STOPA. The stop events at the input pin are distributed alternatingly between the combined channels. Readout is indicated via FRAME or INTERRUPT pins when both channels have results in their FIFO. The advantage of combining channels lies in improved pulse-to-pulse spacing

- Excellent pulse-to-pulse spacing

- Doubled FIFO depth per stop input pin

- Higher burst storage capability

- Doubled LVDS readout rate per stop input pin

- HIGH\_RESOLUTION is applicable

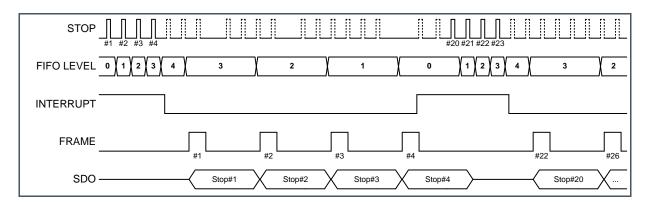

Figure 36:

Channel Combination Low Pulse-to-Pulse Spacing

The outstanding low pulse-to-pulse spacing tpps,CCH is achievable only for a single pulse pair. After a pulse pair, the regular pulse-to-pulse spacing tpps must be awaited, before capturing the next pulse becomes possible. Measurements with HIGH\_RESOLUTION will increase the regular pulse-to-pulse spacing but the low pulse-to-pulse spacing tpps,CCH is not affected.

Figure 37:

Channel Combination Low Pulse-to-Pulse Spacing

## Information

- With LVDS outputs the FRAME pins of combined channels are active together.

- SPI readout of combined channel pairs is permitted only pairwise like CHA-CHB-CHA-CHB-.

But it is not permitted to read one channel twice like CHA-CHA-CHB-CHB-.

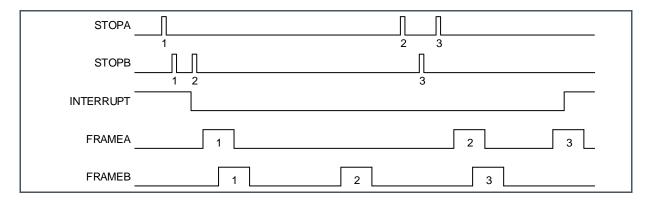

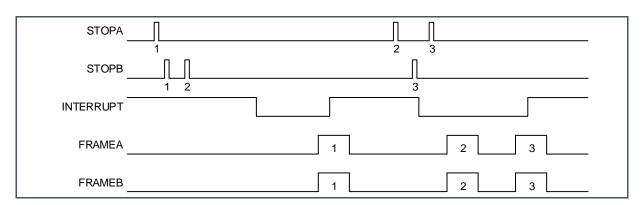

#### 8.3.2 Channel Combination for Pulse Width Measurement

With CHANNEL\_COMBINE set to "PULSE\_WIDTH" the two internal stop channels A & B are connected to one input pin STOPA. The rising edges are measured by channel A, falling edges are measured by channel B. Readout starts on both channels simultaneous when a rising and falling edge was measured.

HIGH\_RESOLUTION or COMMON\_FIFO\_READ is fully applicable

Figure 38: Channel Combination Pulse Width Measurement

**Note:** For internal processing reasons, after the conversion latency t<sub>PPS</sub> the next pulses can be captured earliest. Measurements with HIGH\_RESOLUTION will increase the conversion latency but minimum pulse width t<sub>PWH,STOP</sub> is not affected.

Figure 39: Channel Combination Pulse Width Measurement

- With LVDS output the FRAME pins of combined channels are active together.

- SPI readout of combined channel pairs is permitted only pairwise like CHA-CHB-CHA-CHB-.

But it is not permitted to read one channel twice like CHA-CHB-CHB-.

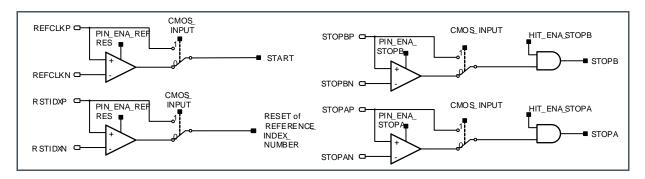

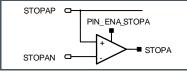

## 8.4 Input Pins for Time Measurement

The following diagram show the relevant input pins for the reference and the stops.

Figure 40: Input Circuitry

### 8.4.1 REFCLKP/N: Reference Clock Input

The reference clock serves as universal time base. Due to internal averaging, the phase jitter of the reference clock is non-critical. The accuracy and drift of the reference clock also does not affect the proper working of AS6501 itself. But it will directly affect the quality of the time measurement results.

### 8.4.2 RSTIDXP/N: Reference Index Counter Reset

With pin RSTIDX the internal counter for the reference index is set back to zero. This option may simply the overview on the reference index in the output data stream. RSTIDX is applied synchronously to the reference clock for at least a single period. After release of RSTIDX, one reference clock cycle passes before stop events are assigned with zero as reference index. The pin has to be activated with PIN\_ENA\_RSTIDX.

Figure 41:

Reference Index Counter Reset

#### 8.4.3 STOPAP/N, STOPBP/N: Stop Channels

Inputs for the stop signals. The positive edges of the stop signals are measured versus the preceding reference clock edge.

The chip has two independent stop channels. With CHANNEL\_COMBINE variations of this normal operation mode can be achieved.